# Оптимизация микропрограммного устройства управления с преобразователем адреса микрокоманд

Баркалов А.А. University of Zielona Gora (Poland) A.Barkalov@iie.uz.zgora.pl

Зеленёва И.Я., Лаврик А.С. Кафедра ЭВМ ДонНТУ

### Аннотация

Баркалов А.А., Зеленёва И.Я., Лаврик А.С. Оптимизация микропрограммного устройства управления с преобразователем адреса микрокоманд. В работе предложен метод уменьшения аппаратурных затрат в логической схеме композиционного микропрограммного устройства управления при реализации на СРLD. Метод базируется на использовании большого коэффициента объединения по входу макроячеек РАL, что позволяет использовать больше одного источника для адреса микрокоманды. Такой подход позволяет минимизировать количество макроячеек РАL, которые используются для преобразования адреса микрокоманды. Приведены условия и результаты экспериментов.

## Анотація

Баркалов О.О., Зеленьова І.Я., Лаврік О.С. Оптимізація мікропрограмного пристрою керування с перетворювачем адреси мікрокоманд. В роботі запропоновано метод зменшення апаратурних витрат у логічній схемі композиційного мікропрограмного пристрою керування при реалізації на СРLD. Метод базується на використанні великого коефіцієнту об'єднання за входом у макрокомірок РАL, що дозволяє використовувати більше ніж одне джерело для адреси мікрокоманди. Такий підхід дозволяє мінімізувати кількість макрокомірок РАL що використовуються для перетворювання адреси мікрокоманди. Наведено умови та результати експериментів.

#### **Abstract**

Barkalov A.A., Zelenyova I.Y., Lavrik A.S. Application of PLD features for optimization of the microprogram control unit logical circuit. The method of hardware reduction is proposed oriented on compositional microprogram

control units and CPLD chips. The method is based on a wide fan-in of PAL macrocells allowing using more than one source of microinstruction address. Such approach permits to minimize the number of PAL macrocells used for transformation of microinstruction address. Conditions for this method application and results of experiments are given.

#### Введение

Одним из важных блоков цифровых систем является устройство управления [1]. Если реализуемый алгоритм имеет линейный характер [2], интерпретации может быть использована композиционного микропрограммного устройства управления (КМУУ) [2]. В настоящее время для реализации схем устройств управления широко используются программируемые логические интегральные схемы (ПЛИС), состоящие из макроячеек программируемой матричной логики (ПМЛ) [3, 4]. Высокая стоимость этого базиса требует решения актуальной задачи уменьшения числа микросхем ПЛИС в схеме КМУУ. Один из путей решения этой задачи – уменьшение числа термов в дизъюнктивных нормальных формах (ДНФ) реализуемых функций [5, 6]. В настоящей работе предлагается возможный подход к решению этой задачи, основанный на большом коэффициенте объединения по входу (порядка нескольких десятков) макроячеек ПМЛ [3, 4]. Разработанный метод ориентирован на КМУУ с преобразователем адреса микрокоманд [2], при этом алгоритм управления представлен в виде граф-схемы алгоритма  $(\Gamma CA)$  [7].

<u>Целью</u> исследования является оптимизация комбинационной схемы КМУУ за счёт использования нескольких источников кодов классов псевдоэквивалентных операторных линейных цепей (ОЛЦ). <u>Задачей</u> исследования является разработка метода синтеза, позволяющего уменьшить число макроячеек ПМЛ в схеме преобразователя адреса микрокоманды.

# Особенности КМУУ с преобразователем адреса

Пусть ГСА Г представлена множествами вершин В и дуг Е, соединяющих эти вершины. При этом  $B = \{b_0, b_E\} \cup E_1 \cup E_2$ , где  $b_0$  - начальная вершина ГСА,  $b_E$  - конечная вершина ГСА,  $E_1$  - множество операторных вершин, где  $|E_1| = M$ ,  $E_2$  - множество условных вершин. В вершинах  $b_q \in E_1$  записаны наборы микроопераций  $Y(b_q) \subseteq Y$ , где  $Y = \{y_1, ..., y_N\}$  - множество микроопераций. В вершинах  $b_q \in E_2$ , записаны элементы множества логических условий  $X = \{x_1, ..., x_L\}$ . Пусть ГСА Г является линейной, то есть включает более 75% операторных вершин [2].

Сформируем множество ОЛЦ  $C = \{\alpha_1,...,\alpha_G\}$  ГСА  $\Gamma$ , где каждая из ОЛЦ является последовательностью операторных вершин и каждой паре её соседних компонент  $b_i,b_j$  соответствует дуга  $\langle b_i,b_j\rangle \in E$ . Каждая ОЛЦ имеет только один выход  $O_g$  и произвольное число входов (g=1,...,G). Формальные определения ОЛЦ, их входов и выходов можно найти в [2]. Каждая вершина  $b_q \in E_1$  соответствует микрокоманде  $MI_q$ , хранимой в управляющей памяти (УП) КМУУ по адресу  $A(b_q)$ . Для адресации микрокоманд достаточно

$$R = \lceil \log_2 M \rceil \tag{1}$$

бит, представленных переменными  $T_r \in T$ , где |T| = R. Пусть ОЛЦ  $\alpha_g \in C$  включает  $F_g$  компонент, а адресация микрокоманд выполнена так, что

$$A(b_{gi+1}) = A(b_{gi}) + 1,$$

(2)

где  $b_{gi}$  - i-я компонента ОЛЦ $\alpha_g \in C$  ,  $i=1,...,F_g-1$  .

Если выходы  $O_i, O_j$  соединены с входом одной и той же вершины ГСА  $\Gamma$ , то ОЛЦ  $\alpha_i, \alpha_j \in C$  являются псевдоэквивалентными ОЛЦ (ПОЛЦ) [2]. Найдём разбиение  $\Pi_C = \{B_1, ..., B_I\}$  множества  $C_1 \subseteq C$  на классы ПОЛЦ. При этом ОЛЦ  $\alpha_g \in C_1$ , если её вход не связан с вершиной  $b_E$ , то есть  $\left\langle O_g, b_E \right\rangle \notin E$ . Закодируем классы  $B_i \in \Pi_C$  двоичными кодами  $K(B_i)$  разрядности

$$R_1 = \lceil \log_2 I \rceil \tag{3}$$

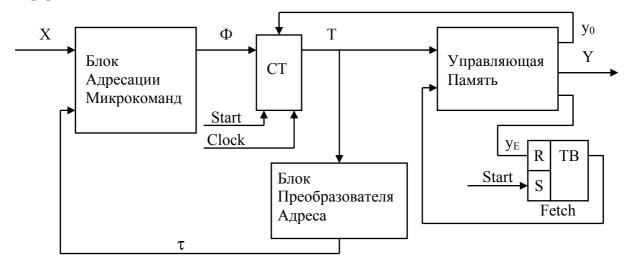

и используем для кодирования элементы множества  $\tau$ , где  $|\tau| = R_1$ . В этом случае для интерпретации ГСА  $\Gamma$  может быть использовано КМУУ с преобразователем адреса (Рис. 1), обозначаемое в дальнейшем символом  $U_1[2]$ .

Рисунок 1 — Структурная схема КМУУ  $U_1$

По сигналу Start в счётчик (СТ) записывается начальный адрес микропрограммы, а триггер выборки (ТВ) устанавливается в единичное состояние. При этом Fetch = 1, что разрешает выборку микрокоманд из УП. Если считанная микрокоманда  $MI_q$  не соответствует выходу ОЛЦ  $\alpha_g \in C_1$ , то одновременно с микрооперациями  $Y(b_q)$  формируется переменная  $y_0$ . Если  $y_0 = 1$ , то содержимое СТ увеличивается на 1, что соответствует режиму безусловного перехода (2) в пределах ОЛЦ. В противном случае  $y_0 = 0$  и блок адресации микрокоманд (БАМ) формирует функции

$$\Phi = \Phi(\tau, X) \tag{4}$$

для записи в СТ адреса входа очередной ОЛЦ. При этом блок преобразователя адреса (БПА) формирует функции

$$\tau = \tau(T),\tag{5}$$

равные единице в коде  $K(B_i)$ , где  $\alpha_g \in B_i$ . Если достигнут выход ОЛЦ  $\alpha_g \notin C_1$ , то формируется  $y_E = 1$ , триггер ТВ обнуляется и выборка микрокоманд прекращается.

Такая организация КМУУ позволяет уменьшить число термов в системе функций  $\Phi$  от  $H_1$  до  $H_0$ , где  $H_1$  — число строк таблицы переходов автомата Мура, а  $H_0$  — число строк таблицы переходов эквивалентного автомата Мили. Однако, схема БПА потребляет некоторые ресурсы ПЛИС или ППЗУ, из которых строится УП. В настоящей работе предлагается метод синтеза КМУУ  $U_2$ , в котором  $H_2$ = $H_0$ , а схема БПА требует меньше аппаратурных затрат, чем в КМУУ  $U_1$ . При определённых условиях этот блок может вообще исчезнуть.

# Основная идея предлагаемого метода

Отметим, что схемы блоков БАМ, БПА, СТ и ТВ реализуются в составе ПЛИС, а для реализации УП требуются ППЗУ, имеющие t выходов (t=1,2,4,8,16). Выполним адресацию ОЛЦ  $\alpha_g \in C_1$  таким образом, чтобы выполнялось (2) и максимально возможное число классов  $B_i \in \Pi_C$  выражалось одним обобщённым интервалом R-мерного булева пространства. Для такой адресации необходимо разработать алгоритм.

Пусть  $\Pi_C = \Pi_A \cup \Pi_B$ , где  $B_i \in \Pi_A$ , если этому классу соответствует один интервал, и  $B_i \in \Pi_B$  в противном случае. Источником кодов для классов  $B_i \in \Pi_A$  является счётчик СТ. Если выполняется условие

$$\Pi_{B} = \emptyset \,, \tag{6}$$

то блок БПА отсутствует. В противном случае преобразованию подлежат только адреса выходов ОЛЦ, входящих в классы  $B_i \in \Pi_B$ . Для кодирования этих классов достаточно

$$R_2 = \lceil \log_2(I_B + 1) \rceil \tag{7}$$

переменных, где  $I_B = |\Pi_B|$ , единица прибавляется для кодирования ситуации  $B_i \in \Pi_A$ . Отметим, что часть кодов может быть реализована на свободных выходах ППЗУ. Пусть для кодирования микроопераций используется стратегия унитарного кодирования [2], тогда слово УП имеет N+2 разрядов. Для реализации УП требуется

$$R_0 = \left\lceil \frac{N+2}{t} \right\rceil \tag{8}$$

микросхем с числом ячеек, не меньшим М. При этом

$$R_3 = R_0 * t - N - 2 \tag{9}$$

выходов ППЗУ являются свободными. Если

$$R_3 \ge R_2 \,, \tag{10}$$

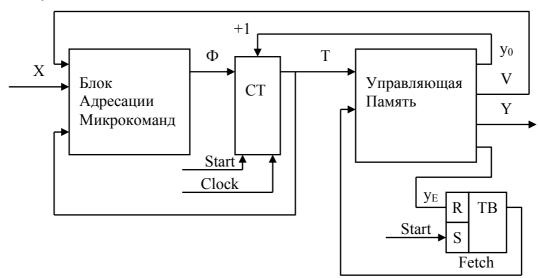

то источниками кодов классов  $B_i \in \Pi_B$  является УП и блок БПА отсутствует. В этом случае для интерпретации ГСА  $\Gamma$  предлагается КМУУ  $U_2$  (Рис. 2).

Рисунок 2 – Структурная схема КМУУ U<sub>2</sub>

В КМУУ  $U_2$  коды  $K_A(B_i)$  классов  $B_i \in \Pi_A$  представляются переменными  $T_r \in T$ , коды  $K_B(B_i)$  классов  $B_i \in \Pi_B$  - переменными  $v_r \in V$ , где  $|V| = R_2$ . В отличие от КМУУ  $U_1$  здесь блок БПА отсутствует, а блок БАМ реализует функции

$$\Phi = \Phi(T, V, X). \tag{11}$$

Пусть символ  $U_i(\Gamma_j)$  означает, что КМУУ  $U_i$  интерпретирует ГСА  $\Gamma_j$ , а  $Q_i(\Gamma_j)$  - число макроячеек в схеме БАМ КМУУ  $U_i(\Gamma_j)$ , где i=1,2. Пусть каждая макроячейка ПМЛ имеет S входов, причём на входы q-й макроячейки КМУУ  $U_i(\Gamma_j)$  поступает  $L_q$  логических условий. Применение предложенного метода целесообразно при выполнении условия

$$L_a + R + R_2 \le S \,, \tag{12}$$

где q = 1, ...,  $Q_1(\Gamma_j)$ . В противном случае число  $Q_2(\Gamma_j)$  значительно увеличивается по сравнению с  $Q_1(\Gamma_j)$ .

В настоящей работе предлагается метод синтеза КМУУ  $U_2$ , включающий следующие этапы.

- 1. Формирование множеств C,  $C_1$ ,  $\Pi_C$  для  $\Gamma$ СА  $\Gamma$ .

- 2. Адресация микрокоманд.

- 3. Формирование множеств  $\Pi_{A}$ ,  $\Pi_{B}$ .

- 4. Кодирование классов  $B_i \in \Pi_B$ .

- 5. Формирование содержимого управляющей памяти.

- 6. Формирование таблицы переходов КМУУ.

- 7. Синтез логической схемы КМУУ.

## Исследование эффективности предложенного метода.

Найдём область эффективного применения КМУУ  $U_2$ , используя для этого вероятностный подход, рассмотренный в [2]. Согласно этому подходу каждая ГСА  $\Gamma$  характеризуется долей операторных вершин  $P_1$ . в случае линейных ГСА  $P_1 \geq 0.75$ . В исследовании используются матричные модели КМУУ [7], а не схемы в определённом базисе. При этом аппаратные затраты характеризуются площадью матриц, занимаемых схемах. Вывод об эффективности предложенного метода делается на основании исследования отношения

$$f = \frac{S(U_2)}{S(U_1)},\tag{13}$$

где  $S(U_i)$  - площадь матричной реализации КМУУ  $U_i$  (i=1,2).

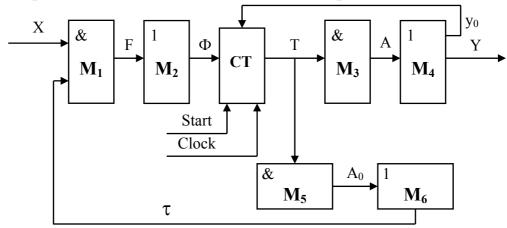

Матричная модель КМУУ  $U_1$  показана на рис. 3.

Рисунок 3 — Матричная реализация КМУУ  $U_1$

В этой схеме конъюнктивная матрица  $M_1$  реализует систему F термов функций  $\Phi$ , а дизъюнктивная матрица  $M_2$  реализует функции (4). Конъюнктивная матрица  $M_3$  реализует полный дешифратор, имеющий R входов, выходы которого представляют адреса микрокоманд, образующие множество A. Дизъюнктивная матрица  $M_4$  реализует функции уз множества  $\{Y, y_0, y_E\}$ . Конъюнктивная матрица  $M_5$  реализует термы, соответствующие адресам выходов ОЛЦ и образующие множество  $A_0$ . Дизъюнктивная матрица  $M_6$  реализует функции системы (5). Итак, матрицы  $M_1$  и  $M_2$  представляют блок БАМ, матрицы  $M_3$  и  $M_4$  – управляющую память, а матрицы  $M_5$  и  $M_6$  – блок БПА. Площади  $S(M_j)$  этих матриц можно определить следующим образом:

$$S(M_1)_{1} = 2(L + R_1) * H_0; S(M_2)_{1} = H_0 * R;$$

$$S(M_3)_{1} = 2R * 2^R; S(M_4)_{1} = 2^R (N + 2);$$

$$S(M_5)_{1} = 2R * G; S(M_5)_{1} = G * R_1;$$

(14)

матричная реализация КМУУ  $U_2$  отличается от рис. 3. отсутствием матриц  $M_5$  и  $M_6$ , так как выполняется (10). При этом число макроячеек ПМЛ в схемах БАМ для КМУУ  $U_1$  и  $U_2$  одинаково. Это позволяет записать следующее равенство

$$S(M_j)_1 = S(M_j)_2 \quad (j = 1,...,4).$$

(15)

В формулах  $S(M_j)_i$  индекс i подчёркивает, что речь идёт о КМУУ  $U_i$  (i = 1,2). Теперь функция (13) может быть выражена как

$$f = \begin{bmatrix} \sum_{j=1}^{4} S(M_j)_2 \end{bmatrix} : \begin{bmatrix} \sum_{j=1}^{6} S(M_j)_1 \end{bmatrix}. \tag{16}$$

Выразим переменные функции (13), используя результаты работы [2]. Пусть К – число вершин ГСА Г, тогда

$$R = \lceil \log_2 p_1 K \rceil \tag{17}$$

Блок БАМ представляет собой автомат Мура, имеющий

$$G = k_1 p_1 K \tag{18}$$

состояний, где  $k_1 < 1$ . При этом параметр  $R_1$  определяется формулой

$$R_1 = \lceil \log_2 k_2 G \rceil, \tag{19}$$

где  $k_2 < 1$ , а произведение  $k_2 G$  определяет число классов I.

Следующие формулы могут быть использованы для определения параметров L и  $H_0$ .

$$L = (1 - p_1)K/1,3; (20)$$

$$H_0 = 4,4 + 1,1k_2G. (21)$$

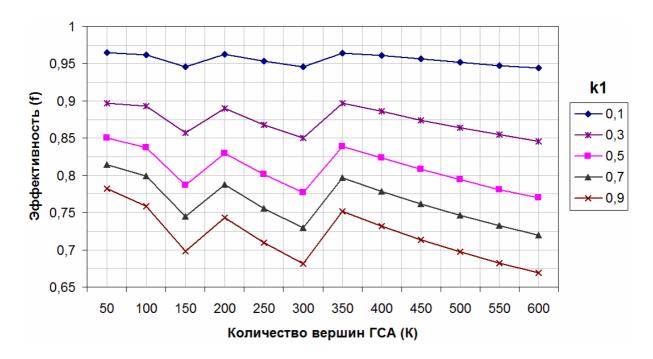

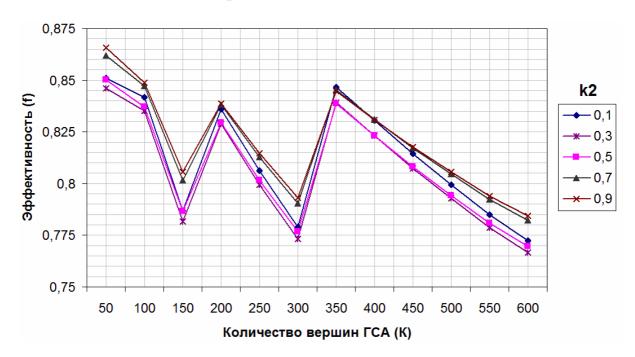

Теперь функция (16) зависит от параметров K,  $p_1$ ,  $k_1$ ,  $k_2$ , N. Некоторые результаты наших экспериментов приведены на рис. 4 и рис. 5.

Рисунок 4 — Зависимость эффективности применения предложенной структуры от количества вершин ГСА при разном значении  $k_1$  ( $p_1 = 0.75, k_2 = 0.5, N = 5$ )

Рисунок 5 — Зависимость эффективности применения предложенной структуры от количества вершин ГСА при разном значении  $k_2$  ( $p_1=0.75,\,k_1=0.5,\,N=5$ )

Как следует рис. 4,5, при выполнении условия (10) КМУУ  $U_2$  всегда требует меньше аппаратурных затрат, чем КМУУ  $U_1$ . При этом выигрыш увеличивается по мере увеличения коэффициента  $k_1$ . Влияние

коэффициента  $k_2$  неравномерно и очень мало. Средний выигрыш при K=300,  $p_1=0.75$ ,  $k_1=0.5$ ,  $k_2=0.5$  и N=5, составляет 13 %.

#### Заключение

Предлагаемый в работе метод оптимизации КМУУ ориентирован на уменьшение числа макроячеек ПМЛ в логической схеме устройства. Уменьшение аппаратурных затрат достигается за счёт использования двух источников кодов преобразования адресов, что возможно при выполнении условия (10).

<u>Научная</u> новизна предложенного метода заключается В особенностей базиса ПЛИС. использовании a именно коэффициента объединений по входу, для уменьшения аппаратурных затрат в КМУУ. Практическая значимость этого метода заключается в уменьшении числа микросхем при реализации схемы КМУУ, что позволяет получить схемы, обладающие меньшей стоимостью сравнению с известными из литературы аналогами. Проведенные нами эксперименты показали, что общее число макроячеек в схеме КМУУ U2 меньше, чем в КМУУ U<sub>1</sub>.

Для повышения эффективности метода необходимо разработать алгоритм адресации микрокоманд КМУУ, уменьшающий число ОЛЦ, адреса выходов которых должны преобразовываться. Это относится к дальнейшему направлению наших исследований, как и проверка возможности использования метода для базиса «систем-на-кристалле» [5], которые имеют внутренние ресурсы для реализации, как произвольной логики, так и управляющей памяти КМУУ.

# Литература

- 1. DeMicheli G. Synthesis and Optimization of Digital Circuits. McGraw-Hill, 1994. 636 pp.

- 2. Баркалов А.А. Синтез устройств управления на программируемых логических устройствах. Донецк: ДНТУ, 2002. 262 с.

- 3. Электронный pecypc. Altera devices overview. http://www.altera.com/products/devices/common/dev-family overview.html.

- 4. Электронный pecypc. Xilinx CPLDs http://www.xilinx.com/products/silicon\_solutions/cplds/index.htm.

- 5. Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем с использованием микросхем программируемой логики. СПб: БХВ. Петербург, 2002. 608 с.

- 6. Соловьев В.В. Проектирование цифровых схем на основе программируемых логических интегральных схем. М.: Горячая линия-ТЕЛЕКОМ, 2001. 636 с.

7. Baranov S. Logic Synthesis for Control Automata. – Kluwer Academic Publishers, 1994. – 312 pp.

Баркалов Александр Александрович.

Д.т.н., профессор, профессор кафедры ЭВМ ДонНТУ, профессор Университета Зеленогурского (Польша).

Научные интересы: Цифровые устройства управления.

Зеленёва Ирина Яковлевна. К. т. н., доцент, доцент кафедры ЭВМ ДонНТУ. Научные интересы: Экспертные системы, цифровые устройства управления.

**Лаврик Александр Сергеевич**. Ассистент кафедры ЭВМ ДонНТУ. Научные интересы: Цифровые устройства управления.