## 1. МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ПРОЕКТИРОВАНИЮ БЛОКОВ ОБРАБОТКИ ДАННЫХ

Микропроцессорная секция К1804ВС1

Микропроцессорная секция (МПС) К1804ВС1 предназначена для приема, оперативного хранения и обработки двоичной информации. Одна секция имеет четыре разряда. При соединении п БИС МПС возможна обработка 4 n - разрядных слов с последовательным и параллельным (при применении схемы ускоренного переноса) переносом.

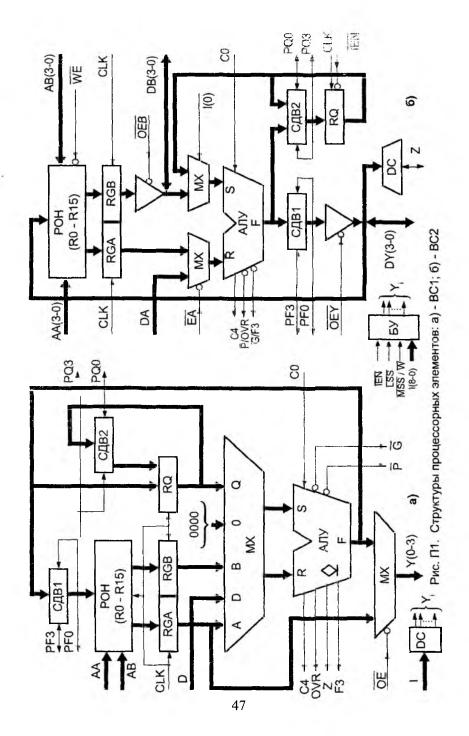

Структурная схема МПС приведена на рис. П1, а. В ее состав входят: АЛУ, блок РОН, два сдвигателя (СДВ1 и СДВ2), два буферных регистра (RGA и RGB), два мультиплексора (МХ), рабочий регистр RQ и декодер микрокоманд DC. На структурной схеме приняты следующие обозначения:

| AA (3-0)     | - входы адреса РОН по каналу А;               |

|--------------|-----------------------------------------------|

| AB (3-0)     | - входы адреса РОН по каналу В;               |

| 1(8-0)       | - входы кода микрокоманды;                    |

| CLK          | - вход синхронизации;                         |

| PF3, PF0, F  | PQ3 , PQ0 - двунаправленные цепи сдвига       |

|              | информации в АЛУ и рабочем регистре RQ;       |

| D(3-0)       | - информационный вход;                        |

| Y(3-0)<br>OE | - информационный выход с тремя состояниями;   |

| OE           | - вход управления выдачей информации;         |

| C0           | - вход переноса АЛУ;                          |

| C4           | - выход переноса АЛУ;                         |

| Z            | - выход (с открытым коллектором) признака     |

|              | нулевого результата АЛУ;                      |

| OVR          | - выход признака переполнения результата АЛУ; |

параллельного переноса и формирования местного группового переноса.

Основными элементами структурной схемы МПС К1804ВС1

- выходы разрешения распространения

- выход знака результата (старший разряд АЛУ);

являются блок РОН (16 регистров по 4 разряда каждый ) с двумя выходными портами и быстродействующее АЛУ.

Под управлением 4 - разрядного адресного слова, поданного на вход АА, любое из 16 слов РОН может быть считано через порт А.

Одновременно через выходной порт В можно производить считывание любого регистра РОН, определяемого адресным

словом АВ. Запись новой информации в РОН может производиться только по адресу АВ. Данные поступают в РОН через сдвигатель СДВ1. Это позволяет , когда требуется , производить сдвиг выходных данных АЛУ ( шина  $\, {\sf F} \,$  ) на один разряд вправо или влево при записи  $\, {\sf F} \,$  в РОН без сдвига.

К обоим выходным портам РОН подключены буферные регистры RGA и RGB для исключения "гонок при записи новых данных в РОН

АЛУ может выполнять три арифметических и пять логических операций над двумя 4 - разрядными словами R и S , данные на которые подаются через мультиплексор МХ. Такая схема подключения дает возможность выбирать различные пары сигналов A , B , D , Q и 0 в качестве операндов АЛУ (см. табл. П1).

Таблица П1 Выбор источников операндов АЛУ

| Мик            | роком | анда           | Исто | чники |

|----------------|-------|----------------|------|-------|

| I <sub>2</sub> | I,    | I <sub>o</sub> | R    | S     |

| 0              | 0     | 0              | Α    | α     |

| 0              | 0     | 1              | Α    | В     |

| 0              | 1     | 0              | 0    | α     |

| 0              | 1     | 1              | 0    | В     |

| 1              | 0     | 0              | 0    | Α     |

| 1              | 0     | 1              | D    | A     |

| 1              | 1     | 0              | D    | Q     |

| 1              | 1     | 1              | D    | 0     |

Рабочий регистр RQ (аккумулятор) предназначен для реализации операций умножения и деления, а также может быть использован в качестве аккумулятора. С помощью сдвигателя СДВ2 содержимое регистра RQ может быть сдвинуто на один разряд влево или вправо.

Выбор операций АЛУ и приемников результата производится в соответствии с табл. П2 - табл. П3.

Для каскадного соединения нескольких БИС служат сигналы входного С0 и выходного С4 переносов. С целью установления факта получения нулевого результата необходимо объединить выходы Z всех микропроцессорных секций по схеме проводного "ИЛИ". Когда все выходы F АЛУ принимают нулевое состояние, на выходе Z устанавливается высокий уровень сигнала.

Выбор операции АЛУ

| Микр | о ко м | анда | Операция                    |

|------|--------|------|-----------------------------|

| I,   | I,     | I,   | Операция                    |

| 0    | 0      | 0    | F = R + S + C0              |

| 0    | 0      | 1    | F = S + R + C0              |

| 0    | 1      | 0    | $F = R + \overline{S} + C0$ |

| 0    | 1      | 1    | F = R ∨ S                   |

| 1    | 0      | 0    | F = R ^ S                   |

| 1    | 0      | 1    | F = R \ S                   |

| 1    | 1      | 0    | F = R ⊕ S                   |

| 1    | 1      | 1    | F = (R ⊕ S)                 |

Таблица ПЗ Выбор приемников результата АЛУ

| Микр           | икрокоманд-<br>а |                | РОН    |                        |        | RQ                    | Выход |

|----------------|------------------|----------------|--------|------------------------|--------|-----------------------|-------|

| I <sub>a</sub> | I,               | I <sub>6</sub> | Сдвиг  | Загрузка               | Сдвиг  | Загрузка              | ٧     |

| 0              | 0                | 0              |        | -                      | _      | $F \rightarrow RQ$    | F     |

| 0              | 0                | 1              |        | -                      | -      | -                     | F     |

| 0              | 1                | 0              | -      | $F \to R(B)$           | _      | -                     | Α     |

| 0              | 1                | 1              | -      | $F \rightarrow R(B)$   |        | -                     | F     |

| 1              | 0                | 0              | Вправо | $F/2 \rightarrow R(B)$ | Вправо | $RQ/2 \rightarrow RQ$ | F     |

| 1              | 0                | _ 1            | Вправо | F/2 → R(B)             |        | -                     | F     |

| 1              | 1                | 0              | Влево  | $2F \rightarrow R(B)$  | Влево  | $2RQ \rightarrow RQ$  | F     |

| 1              | 1                | 1              | Влево  | 2F → R(B)              | -      |                       | F     |

При несовпадении переносов в знаковый и из знакового разрядов АЛУ формируется признак переполнения результата ( на выходе OVR устанавливается высокий уровень напряжения ).

Вывод данных из процессорной секции производится с помощью схем с тремя состояниями , выходы которых Y могут быть подключены к магистрали. Для выдачи данных с порта F АЛУ или с порта A POH необходимо подать сигнал  $\overline{\text{OE}}$  = 0.

Загрузка данных в регистр RQ производится по переднему фронту тактового сигнала CLK, когда имеется разрешение на запись. Если на вход CLK поступает высокий уровень, регистры RGA и RGB находятся в открытом состоянии и пропускают данные с POH. При низком уровне сигнала CLK регистры находятся в состоянии хранения информации. Запись данных в POH производится по адресу AB при низком уровне сигнала CLK.

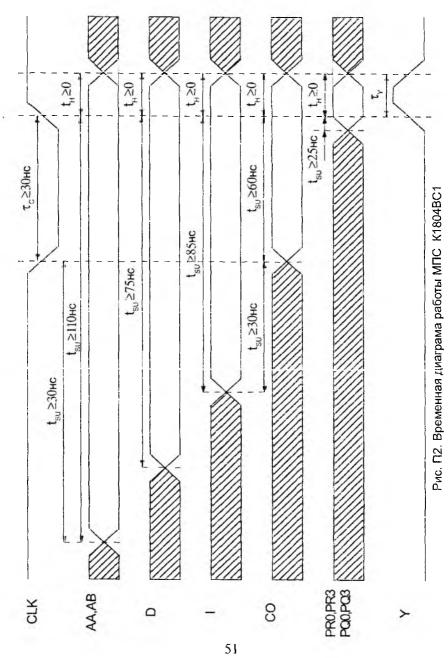

Сигналы признаков C4 , F3 , Z и OVR могут быть поданы на регистр состояния для контроля правильности выполнения вычислений и организации условных переходов в программе. Временная диаграмма работы микропроцессорной секции К1804ВС1 представлена на рис. П2. На временной диаграмме показаны временные соотношения входных и выходных сигналов микропроцессорной секции.

При этом использованы следующие международные обозначения

временных параметров сигналов :

t <sub>(X)</sub> - время задержки выходного импульса относительно входа, указанного в скобках;

$t_{_{SU(y\cdot x)}}$  - время установления сигнала на входе Y до прихода сигнала на входе X;

t <sub>н(у-х)</sub> - время сохранения сигнала на входе Y после окончания сигнала на входе X;

$au_{(x)}$  - минимальная длительность импульса на выходе X. При обозначении  $t_{su}$  первым указывается индекс того входа, по которому сигнал опережает другой, а при обозначении  $t_{\eta}$  первым указывается индекс того входа, на котором сигнал сохраняется после окончания другого.

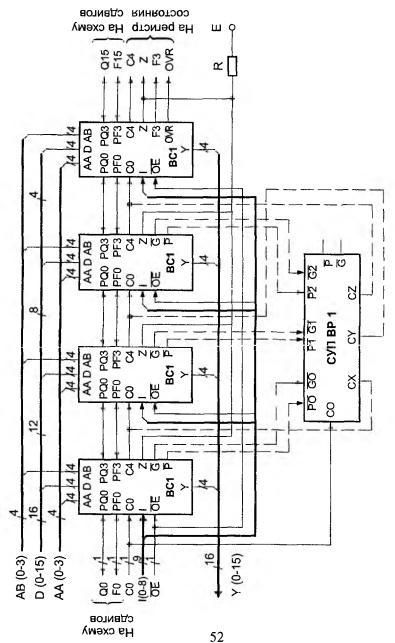

Для организации ускоренных параллельных переносов при выполнении арифметических операций над многоразрядными операндами служит схема ускоренного переноса (СУП) К1804ВР1. Одна схема СУП позволяет организовать параллельные цепи переноса над 16 - разрядными операндами (рис. П3). При разрядности процессора больше 16 может быть использованс каскадное включение СУП. На схеме приняты следующие обозначения входных и выходных сигналов:

- сигнал генерации местного переноса (инверсный сигнал);

СХ , СY, СZ - выходы переносов старшей, средней и младшей групп соответственно; С0 - вход переноса.

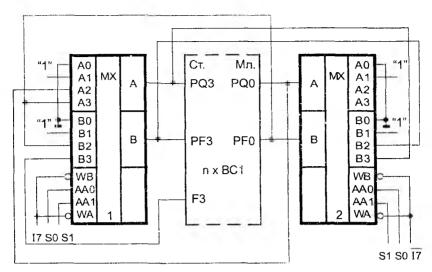

При выполнении сдвиговых операций необходимо с помощью внешних схем организовать коммутацию информации на двунаправленных шинах крайних МПС. Это можно сделать с помощью мультиплексоров с тристабильными выходами (рис. П4). В качестве последних могут быть использованы микросхемы К531КП11 или К555КП12. Седьмой разряд микрокоманды (I , ) используется для управления мультиплексорами, определяя, какой из них, первый или второй, является активным. Выходы неактивного мультиплексора находятся с третьем состоянии и не влияют на функционирование схемы. Сигналы микрокоманды S0 и S1 определяют тип реализуемого сдвига (табл. П4).

Рис. ПЗ. Устройство обработки данных на 16 разрядов.

Рис. П4. Схема организации сдвигов

Таблица П4 Управление сдвигами BC1

| Мик | рокома         | нда | F (выход АПУ)  | RQ (аккумулятор)      |

|-----|----------------|-----|----------------|-----------------------|

| I,  | S <sub>1</sub> | S   | F (REMO)( AID) | V (5 (SVV) WAJIN LOD) |

| 0   | 0              | 0   | "0"            | "0"                   |

| 0   | 0              | 1   | "1"            | **1"                  |

| 0   | 1              | 0   |                | ر الله                |

| 0   | 1              | 1   | "F3"           |                       |

| 1   | 0              | 0   | "0"            | "0"                   |

| 1   | 0              | 1   |                |                       |

| 1   | 1              | 0   |                |                       |

| 1   | 1              | 1   | ·              | "0"                   |

## Микропроцессорная секция К1804ВС2

Микропроцессорная секция K1804BC2 по назначению и принципу построения аналогична БИС K1804BC1 , кроме следующих особенностей:

- наличие АЛУ, выполняющего не только арифметические и логические, но и специальные функции;

- наличие сдвигателя данных АЛУ, выполняющего логические и арифметические сдвиги;

- наличие встроенных схем для программно аппаратной реализации умножения, деления, нормализации, преобразования в дополнительный код и других операций;

- наличие двух дополнительных двунаправленных шин ввода вывода информации.

Структурная схема МПС K1804BC2 показана на рис. П1 , б. Микропрограммирование БИС выполняется в соответствии с табл. П5 - табл. П8.

Таблица П5

Источники операндов АЛУ

| Код | нав | ходе | Источ | ники |

|-----|-----|------|-------|------|

| EA  | 1,  | OEB  | R     | S    |

| 0   | 0   | 0    | RGA   | RGB  |

| 0   | 0   | 1    | RGA   | DB   |

| 0   | 1   | *    | RGA   | RQ   |

| 1   | 0   | 0    | DA    | RGB  |

| 1   | 0   | 1    | DA    | DB   |

| 1   | 1   | *    | DA    | RQ   |

В качестве операндов R и S АЛУ в зависимости от управляющих сигналов  $\overline{EA}$ ,  $\overline{OEB}$  и  $I_0$  могут быть выбраны из POH, рабочего регистра RQ или с шин DA и DB. Перечень микроинструкций, выполняемых АЛУ над операндами R и S с учетом входного переноса CO, и в зависимости от кода микрокоманды  $I_4$  . . .  $I_0$  приведен в табл. П6.

АЛУ обеспечивает выполнение семи арифметических, девяти логических операций и девяти специальных функций над одним или двумя 4 - разрядными входными операндами ( R и S ), поступающих с выходов мультиплексоров.

Выбор приемника результата АЛУ ( РОН выход DY или регистр RQ ), вида и направления сдвига производится сигналами  $\mathbf{I}_8 \dots \mathbf{I}_5$  кода микрокоманды, при условии, что хотя бы один из разрядов  $\mathbf{I}_4 \dots \mathbf{I}_9$

принимает значение " 1 " и управляющий сигнал  $\overline{\text{EN}}$  = 0 (см.  $\underline{\text{табл}}$ .  $\Pi$ 7). Выходные данные АЛУ выводятся на выход DY БИС при  $\overline{\text{OEY}}$  = 0. Одновременно они могут быть записаны в POH по адресу AB.

Сдвигатель данных АЛУ, в отличие от сдвигателя регистра RQ, кроме описанных логических сдвигов, когда все разряды сдвигаются одинаково, может выполнять и арифметические сдвиги. Арифметические сдвиги выполняются также, как и логические, за исключением того, что старший (знаковый) разряд старшей МПС не участвует в сдвигах. Когда сдвиги не выполняются выводы сдвигателей PF3, PF0, PQ3 и PQ0 находятся в третьем состоянии.

Формирователь признака нуля вырабатывает сигнал состояния Z. Наличие " 1 " на этом выводе означает , что все сигналы на выходах АЛУ, или на выходах RQ, или на выходах AЛУ и на выходах RQ нулевые.

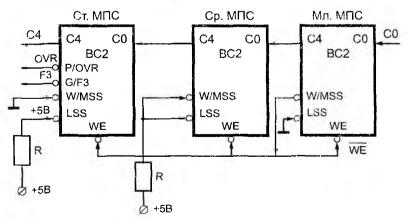

Выход старшего разряда результата АЛУ ( F3 ) и выход переполнения (OVR) используются только в старшей МПС. Поэтому в МПС используются объединенные выходы G/F3 и P/OVR, которые действуют как G и P для средних и младших МПС и как F3 и OVR - для старшей. Поэтому при соединении МПС необходимо выполнить настройку на заданное положение (старшая, средняя или младшая МПС). Такая настройка осуществляется с помощью шин LSS и  $\overline{MSS}/W$ .

В младшей МПС на входе  $\overline{LSS}$  устанавливается "0 ". При этом шина  $\overline{MSS}$  / $\overline{W}$  становится выходом ( $\overline{W}$ ). Сигнал на выходе  $\overline{W}$  устанавливается в "0 " для каждого такта , в течение которого происходит запись данных в  $\underline{POH}$ . Поэтому обычно входы  $\overline{WE}$  всех МПС соединяют с выходом  $\overline{W}$  младшей  $\underline{MПC}$  , как показано на рис.  $\overline{\PiS}$ . В средней и старшей  $\overline{MIC}$  на входе  $\overline{LSS}$  устанавливается "1". При этом шина  $\overline{MSS}$  / $\overline{W}$  становится входом ( $\overline{MSS}$ ). В средней  $\overline{MIC}$  на входе  $\overline{MSS}$  устанавливается "1", а в старшей  $\overline{MIC}$  - "0".

Рис. П5. Схема подключения микросхем ВС2

Таблица П6 Операции АЛУ

Арифметический сдвиг Логич. Лопи. Микрокоманда 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 PF3 0 0 0 0 0 Спец. функции R + S + C0 Функция АЛУ + R + C0 + S + C0 ე + ပ္ပ + 0 0 0 0 ပ္ပ ဗ တ S ഗ S S S 0 **⊕** < > < > Ś œ 1 100 100 œ 12  $\alpha$  $\propto$ S œ S 2 Код микрокоманды 0 × × × × × × × × × × × × 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 56

Таблица П7 Выбор приемника результата ( $\overline{\text{IEN}}$  = 0 ,  $I_0$  V  $I_1$  V  $I_2$  V  $I_3$  V  $I_4$  = 1) JIOTHY. RQ / 2→RQ RQ/2→RQ JOUNY. RQ / 2→RQ JOINY. 2 RQ→RQ JOUNH. 2 RQ→RQ 2 RQ→RQ Функция СДВ2 F→RQ FYRO o ↑o o ↑o o ↑o 040 Ø ↑ Ø Ø **↑**Ø ø≁ø 040 Логи. Логич. 0 ≥ 0 0 0 0 0 0 0 0 0 0 F/2→DY Apuchm. F / 2→DY F / 2→DY F / 2→DY Apuфm. 2 F→DY Арифм. 2 F→DY Функция СДВ1 Логич. 2 F→DY 2 F→DY PF0→DY (0 - 3 (NOP) F→DY F→DY  $F \rightarrow DY$ F→DY トナロイ  $F \rightarrow D Y$ Логич. Арифи.

PF0

PF3,

PF0

сдвиг

Логический

Специальные функции АЛУ БИС К1804ВС2 ( $I_0=I_1=I_2=I_3=I_4=0,\ \overline{\rm IEN}=0$ )

| Σ           | _ <del>Z</del> | Код<br>Ооко<br>Ды | Код<br>микрокоман-<br>ды | Функция АЛУ                           | Операл  | Операция АЛУ  | Операция              | Операция               | еине теми ф        |

|-------------|----------------|-------------------|--------------------------|---------------------------------------|---------|---------------|-----------------------|------------------------|--------------------|

| I           | I,             | -                 | 6 I <sub>5</sub>         |                                       | (Z = 0) | (z = 1)       | сдвигат. г            | CHBMIAI. NO            | 9                  |

| 0           | 0              |                   | 0                        |                                       | s + co  | C0 R+S+C0     | F/2 → DY Логичес.     | RQ/2 → RQ<br>Логическ. | Z=Q(0)<br>PF3=C4   |

| 0           | 0              |                   | 1 0                      | з дополнительн. коде                  | s + C0  | S + C0 R+S+C0 | F/2→DY<br>PF3 =F3⊕OVR | RQ/2 → RQ<br>Логическ. | Z=Q(0)             |

| 0           | -              |                   | 0 0                      | Прибавление 1 или 2                   | S+1+C0  | S+1+C0        | F⇒DY                  | RQ→RQ                  | 1                  |

| 0           | -              |                   | 0 1                      | Преобразован. числа                   | 02 + S  | S + C0        | ¥О←∃                  | RQ→RQ                  | PF3=F3⊕S(3)        |

| 0           | 7              | <u> </u>          | 0                        | Коррекция при умножен.                | s + c0  | S+R+C0        | F/2 → DY<br>Логичес.  | RQ/2 → RQ<br>Логическ. | Z=Q(0)<br>PF3=F3⊕V |

| <b>/</b>    | 0              |                   | 0 0                      | Нормализация слова<br>одинарной длины | 00 + S  | S + C0        | F→DY                  | 2RQ→RQ<br>Логическ.    | _                  |

| <del></del> | 0              | · -               | 0                        | Нормализация слова<br>двойной длины   | 8 + C0  | s + co        | 2F→DY<br>Логичес.     | 2RQ→RQ<br>Логическ.    | 1                  |

| 7-          | 1              | 0                 | 0 (                      | Деление                               | S+R+C0  | S+R+C0 S+R+C0 | 2F⇒DY<br>Логичес.     | 2RQ→RQ<br>Логическ.    | 1                  |

| +           | -              | -                 | 0                        | в дополнительном коде                 | S+R+C0  | S+R+C0 S+Ř+C0 | F→DY                  | 2RQ→RQ<br>Логическ.    | 1                  |

Микрокоманды с кодами F и E из табл. П7 могут быть использованы для расширения знака . Например , если 16 - разрядный процессор должен интерпретировать 8 - разрядные данные как двоичные числа со знаком , то знаковый разряд расширяется на один байт. Две МПС младшего байта генерируют данные , поэтому на них подается микрокоманда F. Знаковый разряд поступает на шину PF3 второй МПС. На первые две старшие МПС поступает микрокоманда с кодом E. В результате знаковый разряд с шины PF3 передается на все выходы АЛУ двух МПС старшего байта.

Микрокоманды с кодами 4 , 5 , 6 и 7 используются для генерации на шине PF0 сигнала паритета (используется в схемах контроля):

$PF0 = F3 \oplus F2 \oplus F1 \oplus F0 \oplus PF3$ .

Паритетная логика обладает способностью наращивания секций путем соединения вывода PF0 предыдущей МПС с выводом PF3 последующей.

Микропроцессорная секция К1804ВС2 может выполнять девять специальных функций, которые перечислены в табл. П8. Семь кодовых комбинаций не используются и являются запрещенными. При выполнении специальных функций двунаправленный вывод Z в средней и старшей секциях становится входом , на который подается управляющий сигнал [ 1 ], а вывод Z младшей секции выходом.

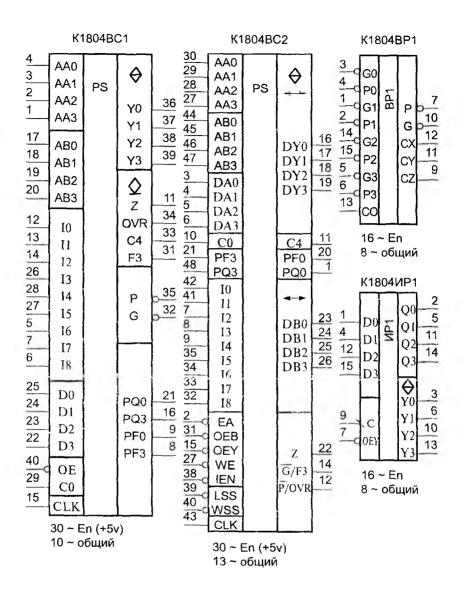

Условные графические обозначения БИС обработки данных представлены на рис. Пб. На этом же рисунке приведено обозначение регистра К1804ИР1, предназначенного для построения регистров различного назначения с разрядностью кратной четырем. Параллельный регистр построен на D - триггерах и имеет две выходные шины: Q - стандартная биполярная и Y - шина с возможностью управления третьим состоянием с помощью сигнала ОЕУ. Запись информации в регистр происходит по переднему фронту сигнала СLК.

Рис. П6. Условные графические обозначения БИС обработки данных