# А.А. Баркалов (докт. техн. наук, проф.) $^1$ , К.Н. Ефименко (канд. техн. наук, доц.) $^2$ , И.Я. Зеленева (канд. техн. наук, доц.) $^2$

Университет Зеленогурский (Польша)<sup>1</sup>, ГВУЗ «Донецкий национальный технический университет» (Украина)<sup>2</sup> E-mail: A.Barkalov@iie.uz.zgora.pl

# ОПТИМИЗАЦИЯ СХЕМЫ АДРЕСАЦИИ КМУУ С ЭЛЕМЕНТАРНЫМИ ЦЕПЯМИ

Предлагается метод уменьшения аппаратурных затрат в схеме КМУУ с элементарными цепями, ориентированный на технологию FPGA. Метод основан на использовании трех источников кодов классов псевдоэквивалентных ЭОЛЦ и мультиплексора, позволяющего выбрать один из этих источников. Такой подход позволит уменьшить число LUT элементов в схеме адресации КМУУ. Приведен пример применения предложенного метода. Ключевые слова: КМУУ, ГСА, ЭОЛЦ, FPGA, логическая схема

### Общая постановка проблемы.

Композиционные микропрограммные устройства управления (КМУУ) являются эффективным средством реализации линейных алгоритмов управления [1,2]. Одной из моделей КМУУ является модель с разделением кодов [3], позволяющая при определенных условиях уменьшить аппаратурные затраты в схеме адресации микрокоманд. В настоящее время микросхемы типа FPGA (field-programmable gate arrays) широко используются при реализации схем цифровых устройств [4,5]. Основу этих СБИС представляют макроячейки табличного типа, называемые LUT (look-up table). Как правило, LUT-элементы имеют ограниченное число входов (4-6) [6,7]. Для уменьшения числа LUT в схеме КМУУ необходимо уменьшить число аргументов и термов в системе функций адресации микрокоманд [1,8]. В настоящей работе предлагается один из подходов к решению этой задачи, основанный на мультиплексировании трех источников кодов классов псевдоэквивалентных элементарных операторных линейных цепей (ЭОЛЦ). Предлагаемый метод является развитием результатов, полученных в работах [9,10].

Целью исследования является уменьшение числа LUT-элементов в схеме КМУУ с элементарными цепями за счет мультиплексирования трех источников кодов классов псевдоэквивалентных ЭОЛЦ.

Задачей исследования является разработка метода синтеза КМУУ с элементарными цепями, позволяющего оптимизировать схему адресации микрокоманд.

Алгоритм управления представлен в виде граф-схемы алгоритма (ГСА) [8]. Этот выбор определен наглядностью подобного представления и широким применением аппарата ГСА в практике инженерного проектирования.

#### Композиционное МУУ с элементарными цепями

Пусть  $\Gamma$ CA  $\Gamma$  =  $\Gamma$ (B,E) представлена множествами вершин B и соединяющих их дуг E. Пусть  $B = b_0 \cup b_E \cup E_1 \cup E_2$ , где  $b_0$  — начальная вершина,  $b_E$  — конечная вершина,  $E_1$  — множество операторных вершин и  $E_2$  — множество условных вершин  $\Gamma$ CA  $\Gamma$ . B операторных вершинах  $b_q \in E_1$  записываются наборы микроопераций  $Y(b_q) \subseteq Y$ , где  $Y = \{y_1,...,y_N\}$  — множество микроопераций. В условных вершинах  $b_q \in E_2$  записываются элементы множества логических условий  $X = \{x_1,...,x_L\}$ . Введем ряд определений, взятых из [2].

Определение 1. Операторной линейной цепью (ОЛЦ) ГСА Г называется конечная по-

следовательность операторных вершин  $\, \boldsymbol{\delta}_g = \left\langle b_{g_1}, ..., b_{g_g} \right\rangle \,$  такая, что для любой пары соседних компонент  $b_{g_i}$ ,  $b_{g_{i+1}}$ , где i – номер компоненты кортежа  $\boldsymbol{\delta}_g$ , существует дуга  $\left\langle b_{g_i}, b_{g_{i+1}} \right\rangle \in E$ .

Определение 2. Вершина  $b_q \in D^g$ , где  $D^g$  — множество вершин, входящих в ОЛЦ  $\delta_g$ , называется входом ОЛЦ  $\delta_g$ , если существует дуга  $\left\langle b_t, b_q \right\rangle$  ∈ E , где  $b_t \notin D^g$  . Элементарная ОЛЦ (ЭОЛЦ) имеет только один вход.

Определение 3. Вершина  $b_q \in D^g$  , называется выходом ОЛЦ  $\delta_g$  , если существует дуга  $\left\langle b_q, b_t \right\rangle \in E$  , где  $b_t \not\in D^g$  .

<u>Определение 4</u>. ЭОЛЦ  $\, {\sf б}_{{}_{i}}, {\sf б}_{{}_{j}} \,$  называются псевдоэквивалентными ЭОЛЦ, если их выходы связаны со входом одной и той же вершины  $\, {\sf b}_{{}_{q}} \in B \, .$

Пусть для некоторой ГСА  $\Gamma$  сформировано множество ЭОЛЦ  $C = \{\delta_1,...,\delta_G\}$ , определяющее разбиение на множестве  $E_1$  [3], и пусть  $\left|E_1\right| = M$ . Поставим в соответствие каждой вершине  $b_q \in E_1$  микрокоманду  $MI_q$  с адресом  $A(b_q)$ , имеющим разрядность

$$R = \lceil \log_2 M \rceil. \tag{1}$$

Пусть  $F_{max} = max(F_1,...,F_G)$  — максимальное число компонент в ЭОЛЦ. Закодируем каждую ЭОЛЦ  $\mathfrak{G}_{\mathfrak{g}} \in C$  двоичным кодом  $K(\mathfrak{G}_{\mathfrak{g}})$ , имеющим  $R_1$  разрядов, где

$$R_1 = \lceil \log_2 G \rceil. \tag{2}$$

Для определения любой вершины  $b_q \in D^g$  достаточно  $R_2$  разрядов, представляющих код  $K(b_q)$  . При этом

$$R_2 = \lceil \log_2 F_{\text{max}} \rceil. \tag{3}$$

Пусть для ГСА Г выполняется следующее условие:

$$R_1 + R_2 = R. (4)$$

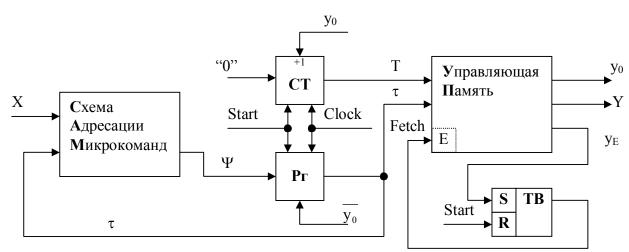

В этом случае для реализации алгоритма  $\Gamma$  целесообразно использовать модель КМУУ с элементарными цепями (Рис. 1).

Рисунок 1 – структурная схема КМУУ с элементарными цепями

В этой модели для кодирования ЭОЛЦ используются переменные  $\tau_r \in \tau$ , где  $|\tau| = R_1$ . Для кодирования компонент ЭОЛЦ используются переменные  $T_r \in T$ , где  $|T| = R_2$ . Коды компонент выбраны так, чтобы выполнялась естественная адресация микрокоманд [1]. Для

этого код первой компоненты любой ЭОЛЦ равен 0, второй -1 и так далее. Естественно, что эти десятичные числа представлены их двоичными  $R_2$ -разрядными эквивалентами.

Условимся в дальнейшем обозначать КМУУ (Рис. 1) символом  $U_1$ .

В КМУУ  $U_1$  схема адресации микрокоманд (CAM) реализует систему функций возбуждения триггера Pr

$$\Psi = \Psi(\tau, X). \tag{5}$$

При этом адрес микрокоманды  $\mathrm{MI}_{\scriptscriptstyle \mathrm{d}}$  представляется в виде

$$A(b_q) = K(\alpha_g) * K(b_q), \tag{6}$$

где вершина  $b_{\mathfrak{q}}$  входит в состав ЭОЛЦ  $\mathfrak{d}_{\mathfrak{g}} \in C$  , \* — знак операции конкатенации.

Композиционное МУУ  $U_1$  функционирует следующим образом. По сигналу Start в Pr и CT заносится начальный адрес микропрограммы, а триггер выборки TB устанавливается в единичное состояние. При этом Fetch = 1, что разрешает выборку команд из управляющей памяти (УП). Если считанная микрокоманда не соответствует выходу ЭОЛЦ, то одновременно с микрооперациями  $Y(b_q)$  формируется сигнал  $y_0$ . Если  $y_0$  = 1, то к содержимому CT прибавляется единица и адресуется следующая компонента текущей ЭОЛЦ. Если выход ОЛЦ достигнут, то  $y_0$  = 0. При этом адрес входа следующей ЭОЛЦ формируется схемой САМ. При достижении окончания микропрограммы формируется сигнал  $y_E$ , триггер TB обнуляется, и выборка микрокоманд прекращается.

Число LUT-элементов в схеме CAM зависит от числа аргументов и термов в системе (5). В настоящей работе предлагается метод, позволяющий уменьшить сложность функций в системе (5) и, следовательно, уменьшить аппаратурные затраты в схеме CAM.

#### Основная идея предлагаемого метода

Пусть ЭОЛЦ  $\mathbf{6}_{\mathrm{g}} \in C_1$ , если  $O_{\mathrm{g}}$  не связан с конечной вершиной ГСА Г. Найдем разбиение  $\Pi_{\mathrm{C}} = \left\{ B_1, ..., B_1 \right\}$  множества  $C_1$  на классы псевдоэквивалентных ЭОЛЦ (ПЭОЛЦ). Выполним кодирование  $\mathbf{6}_{\mathrm{g}} \in C$  так, чтобы максимально возможное число классов  $B_{\mathrm{i}} \in \Pi_{\mathrm{C}}$ , где  $\left| \Pi_{\mathrm{C}} \right| = I$ , представлялось одним обобщённым интервалом  $R_1$ -мерного булева пространства. Пусть  $\mathbf{n}_{\mathrm{i}}$  — число обобщённых интервалов, представляющих класс. Представим множество  $\Pi_{\mathrm{C}}$  в виде  $\Pi_{\mathrm{C}} = \Pi_{\mathrm{A}} \cup \Pi_{\mathrm{B}}$ . При этом множества  $\Pi_{\mathrm{A}}$  и  $\Pi_{\mathrm{B}}$  строятся следующим образом:

$$(n_i = 1) \to B_i \in \Pi_A,$$

$$(n_i > 1) \to B_i \in \Pi_B.$$

$$(7)$$

Источником кодов классов  $B_i \in \Pi_A$  является регистр Pr. При этом код класса  $B_i \in \Pi_A$  определяется соответствующим интервалом  $R_1$ -мерного булева пространства.

Закодируем классы  $B_i \in \Pi_B$  двоичными кодами  $C(B_i)$  разрядности

$$R_3 = \left\lceil \log_2 \left( |\Pi_B| + 1 \right) \right\rceil. \tag{8}$$

Используем для кодирования классов  $B_i \in \Pi_B$  переменные из множества  $Z = \{z_1,...,z_{R_3}\}$ . Для формирования кодов  $C(B_i)$  необходим блок преобразователя кодов (БПК). Этот блок реализует систему функций

$$Z = Z(\tau). (9)$$

Современные микросхемы FPGA имеют в своем составе блоки встроенной памяти EMB (embedded memory block) [6,7]. Эти блоки имеют возможность реконфигурации, которая сводится к изменению числа входов и выходов при фиксированной емкости $V_0$

$$V_0 = 2^S \cdot t_F \,. \tag{10}$$

В формуле (10), переменная S означает число входов, а  $t_F$  число выходов EMB. Как правило, возможны следующие конфигурации современных EMB [6,7]:  $16K\times1$ ,  $8K\times2$ ,  $4K\times4$ ,

$2K\times 8$ ,  $1K\times 16$ ,  $512\times 32$ ,  $256\times 64$  (бит). Это значит, что параметры S и  $t_F$  принадлежат следующим множествам:  $S\in\{14,13,...,8\}$  и  $t_F\in\{1,2,4,8,16,32,64\}$ . При фиксированной величине  $t_F$  число ячеек в EMB определяется следующей формулой:

$$V = \left[ V_0 / t_F \right]. \tag{11}$$

Для реализации УП достаточно M ячеек EMB, При этом блок имеет  $t_{\rm M}$  выходов:

$$\mathbf{t}_{\mathbf{M}} = \left[ \mathbf{V}_{0} / \mathbf{M} \right] \tag{12}$$

Пусть для некоторой  $\Gamma$ CA  $\Gamma$  и микросхемы FPGA имеет место следующее неравенство:

$$N+3+R_3 > t_M > N+3.$$

(13)

В этом случае  $\Delta R = t_M - (N+3)$  разрядов кода  $K(B_i)$  целесообразно формировать на свободных выходах ЕМВ ( $B_i \in \Pi_B$ ). Оставшиеся  $R_3 - \Delta R$  разрядов кода формируются схемой БПК. Это равносильно представлению множества Z в следующем виде:

$$Z = Z^1 \cup Z^2 \,. \tag{14}$$

Переменные  $Z_r \in Z^1$  формируются БПК, а переменные  $Z_r \in Z^2 - УП$ . Очевидно, что пересечение этих множеств пусто.

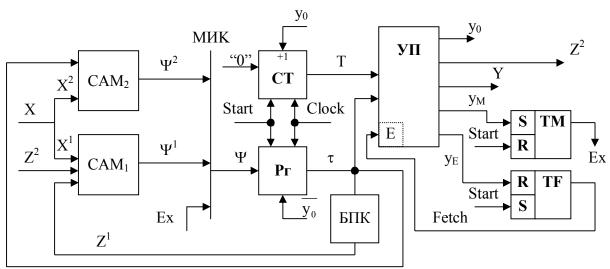

В этом случае для реализации схемы устройства управления предлагается модель КМУУ  $U_2$  (Рис. 2).

Рисунок 2 – структурная схема КМУУ U<sub>2</sub>

Эта модель имеет ряд отличий от модели  $U_1$ . Во-первых, блок CAM разделен на два блока. Блок CAM $_1$  реализует переходы, определяемые множеством  $\Pi_B$ , а блок CAM $_2$  — множеством  $\Pi_A$ . Мультиплексор МИК служит для выбора источника кодов, используя переменную Ex. Значение переменной Ex определяется состоянием триггера TM, управляемого дополнительной переменной  $y_M$ . Блок БПК является источником кодов классов для схемы CAM $_1$ , формируя часть этого кода. Источниками кодов для схемы CAM $_2$  является регистр  $P_\Gamma$ .

Предлагаемое КМУУ функционирует следующим образом. По сигналу Start в Pr и CT заносятся нулевые коды (адрес первой микрокоманды), а триггера TF и TM устанавливаются соответственно в "1" (Fetch = 1) и "0" (Ex = 0). Пока адрес входа не достигнут, то  $U_2$  функционирует как  $U_1$ . При достижении адреса выхода ЭОЛЦ  $\mathbf{6}_{\mathbf{g}} \in \mathbf{B}_{\mathbf{i}}$  может формироваться переменная  $\mathbf{y}_{\mathbf{M}} = 1$ . В этом случае  $\mathbf{E}\mathbf{x} = 1$  и адрес перехода формируется схемой  $\mathbf{CAM}_1$ . Для этого формируется система функций:

$$\Psi^{1} = \Psi^{1}(Z, X^{1}). \tag{15}$$

Если  $B_i \in \Pi_A$ , то переменная  $y_M$  не формируется. При этом Ex = 0 и адрес перехода определяется схемой  $CAM_2$ . Для этого формируется система функций:

$$\Psi^2 = \Psi^2(\tau, X^2). \tag{16}$$

Соответствующие функции передаются на выход МИК и требуемый код  $K(\sigma_g)$  загружается в Pr. Функционирование продолжается обычным образом до формирования переменной  $y_E$  (достижение окончания алгоритма управления).

Такой подход позволяет уменьшить число термов в системе (5) до абсолютного минимума. При выполнении условия

$$R_3 < R_1 \tag{17}$$

уменьшается число аргументов в системе (10) по сравнению с соответствующими функциями из системы (5). Недостатками данного подхода является наличие блоков МИК и БПК, потребляющими некоторые ресурсы кристалла, и увеличение на 1 разрядности слов УП. Однако, схема МИК реализуется за счет использования тристабильных выходов макроячеек, поэтому дополнительных LUT-элементов не требуется.

Очевидно, применение предложенного метода имеет смысл, если число LUT-элементов в блоке БПК будет значительно меньше параметра  $\Delta_{\text{LUT}}$ . Параметр  $\Delta_{\text{LUT}}$  определяется разностью числа LUT-элементов в блоке CAM и блоках CAM $_1$  и CAM $_2$ .

## Особенности реализации схемы КМУУ U2

В настоящей работе предлагается метод синтеза КМУУ  $U_2$ , включающий следующие этапы:

- 1. Формирование для ГСА  $\Gamma$  множеств C,  $C_1$ , и  $\Pi_C$ .

- 2. Оптимальное кодирование ЭОЛЦ  $\, {\bf 6}_{\rm g} \in {\bf C}_1 \,$  и кодирование компонент ЭОЛЦ.

- 3. Формирование множеств  $\Pi_{A}$  и  $\Pi_{B}$ .

- 4. Кодирование классов  $B_i \in \Pi_B$  кодами  $C(B_i)$ .

- 5. Формирование таблицы переходов для классов  $B_i \in \Pi_A$  .

- 6. Формирование таблицы переходов для классов  $\, B_{i} \in \Pi_{\scriptscriptstyle B} \, .$

- 7. Формирование содержимого управляющей памяти.

- 8. Формирование таблицы истинности блока БПК.

- 9. Синтез схемы КМУУ в заданном базисе.

Этапы 1-4 выполняются по известным методикам [1-3]. Этап 9 связан с разработкой VHDL-моделей КМУУ и использованием стандартных промышленных пакетов [6,7]. Эти этапы не представляют особого интереса для иллюстрации синтеза схемы КМУУ  $U_2$ . В этой связи мы не рассматриваем данные этапы в нашей статье.

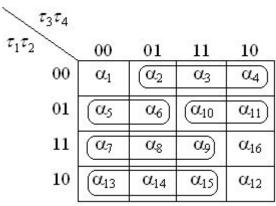

Пусть для некоторой ГСА  $\Gamma_1$  получено множество ЭОЛЦ  $C = \{\delta_1,...,\delta_{16}\}$  и разбиение  $\Pi_C = \{B_1,...,B_7\}$ . При этом  $\delta_{16} \notin C_1$ , а классы  $B_i \in \Pi_C$  определяются следующим образом:  $B_1 = \{\delta_1\}, \ B_2 = \{\delta_2,\delta_3,\delta_4\}, \ B_3 = \{\delta_5,\delta_6\}, \ B_4 = \{\delta_7,\delta_8,\delta_9\}, \ B_5 = \{\delta_{10},\delta_{11}\}, \ B_6 = \{\delta_{12}\}, \ B_7 = \{\delta_{13},\delta_{14},\delta_{15}\}$ . Итак, G = 16,  $R_1 = 4$ ,  $\tau = \{\tau_1,...,\tau_4\}$ .

Оптимальное кодирование ЭОЛЦ  $\[ \[ \] \] \] \] \] б_g \in C_1$  выполняется так, чтобы максимально возможное число классов  $\[ \] \] \] \] б_g \in \Gamma_1$  представлялось одним интервалом  $\[ \] \] \] странства [1]. Один из вариантов кодирования представлен на рис. 3.$

Из карты Карно (Рис. 3) можно получить следующие интервалы, определяющие классы  $B_i \in \Pi_C$ . Класс  $B_1$  определяется интервалом 0000; класс  $B_2$  – интервалами 00\*1 и 001\*; класс  $B_3$  – интервалом 010\*; класс  $B_4$  – интервалами 110\* и 11\*1; класс  $B_5$  – интервалом 011\*; класс  $B_6$  – интервалом 1010; класс  $B_7$  – интервалами 100\* и 10\*1. Таким образом,  $\Pi_A = \{B_1, B_3, B_5, B_6\}$ , где  $K(B_1) = 0000$ ,  $K(B_3) = 010*$ ,  $K(B_5) = 011*$  и  $K(B_6) = 1010$ . Очевидно,

$\Pi_B = \left\{ B_2, B_4, B_7 \right\}$  и для их кодирования необходимо  $R_3 = 2$  разряда. Итак,  $Z = \{z_1, z_2\}$ . Закодируем классы  $B_i \in \Pi_B$  следующим образом:  $C(B_2) = 00$ ,  $C(B_4) = 01$ ,  $C(B_7) = 10$ .

Рисунок 3 — коды ЭОЛЦ  $\, {\sf f}_{\sf g} \in {\sf C} \,$

Таблица переходов формируется на основе обобщённых формул переходов [1]. Пусть, например, из ГСА  $\Gamma_1$  можно получить следующие формулы:

$$\begin{array}{c}

B_{1} \to x_{1}b_{3} \vee \overline{x_{1}}x_{2}b_{8} \vee \overline{x_{1}}\overline{x_{2}}b_{12}; \\

B_{2} \to x_{4}b_{12} \vee \overline{x_{4}}b_{17}.

\end{array} (18)$$

Столбцы таблицы переходов включают следующую информацию: исходный класс (столбец  $B_i$ ); код класса (для  $\Pi_A$  это код  $K(B_i)$ , а для  $\Pi_B - C(B_i)$ ); адрес перехода  $(A(b_q))$ ; логические условия определяющие переход (столбец  $X_h$ ); функции возбуждения триггеров регистра  $P_i$  (столбец  $\Psi_h^1$  для  $\Pi_B$  и  $\Psi_h^2$  для  $\Pi_A$ ); номер перехода (столбец h).

Пусть  $A(b_3) = 000100$ ,  $A(b_8) = 001000$ ,  $A(b_{12}) = 010101$ ,  $A(b_{17}) = 110010$ . Тогда фрагменты таблиц переходов для формул (13) приведены в табл. 1 и табл. 2.

Таблица переходов для класса  $B_1 \in \Pi_A$

|                           |          |          |                                           | 7 1            |   |

|---------------------------|----------|----------|-------------------------------------------|----------------|---|

| $\mathbf{B}_{\mathrm{i}}$ | $K(B_i)$ | $A(b_q)$ | $X_h$                                     | $\Psi_h^2$     | h |

| $B_1$                     | 0000     | 000100   | <b>X</b> <sub>1</sub>                     | $\mathrm{D}_4$ | 1 |

|                           |          | 001000   | $\overline{\mathbf{x}}_{1}\mathbf{x}_{2}$ | $D_3$          | 2 |

|                           |          | 010101   | $\overline{x_1}\overline{x_2}$            | $D_2D_4$       | 3 |

Таблица 2

Таблица 1

Таблица переходов для класса  $B_2 \in \Pi_B$

| $\mathbf{B}_{\mathrm{i}}$ | $C(B_i)$ | $A(b_q)$ | $X_h$                     | $\Psi_h^1$ | h |

|---------------------------|----------|----------|---------------------------|------------|---|

| $\mathrm{B}_{2}$          | 00       | 010101   | X 4                       | $D_2D_4$   | 1 |

|                           |          | 110010   | $\overline{\mathbf{x}_4}$ | $D_1D_2$   | 2 |

Система (15) может быть получена из таблицы переходов для классов  $B_i \in \Pi_B$ . Так, из табл. 2 имеем, например  $D_1 = \overline{z_1} \overline{z_2} \overline{x_4}$ . Система (16) может быть получена из таблицы переходов для классов  $B_i \in \Pi_A$ . Так, из табл. 1, имеем, например,  $D_2 = \overline{\tau_1} \overline{\tau_2} \overline{\tau_3} \overline{\tau_4} \overline{x_1} \overline{x_2}$ .

Пусть из рассматриваемого примера следуют следующие множества:  $Z^1 = \{Z_1\}$  и  $Z^2 = \{Z_2\}$ . При этом БПК реализует только часть кода  $K(B_i)$ . В данном случае реализуется

только разряд  $Z_1$ .

Таблица БПК имеет столбцы:  $B_i$ ,  $K(B_i)_j$ ,  $C(B_i)$ ,  $Z_h$ , h. Здесь  $K(B_i)_j$  – код класса  $B_i$ , соответствующий одному из обобщенных интервалов;  $Z_h$  – разряды кода  $C(B_i)$ , принимающие единичное значение в h-й строке таблицы. Для рассматриваемого примера, число строк  $H_{\Pi K}=6$ . Этот параметр определяется суммарным числом интервалов, представляющих коды классов  $B_i \in \Pi_B$ . Для рассматриваемого примера блок БПК представлен в табл. 3.

Таблица 3

| T ~     | _     | _                    |       |

|---------|-------|----------------------|-------|

| Гаршина | ОПОКа | преобразователя ад   | ппеса |

| таолица | Onora | iipcoopasobaiciin a, | дроса |

|                  | <u> </u>   | 1                  |                | 1 |

|------------------|------------|--------------------|----------------|---|

| $B_{i}$          | $K(B_i)_j$ | C(B <sub>i</sub> ) | $Z_{h}$        | h |

| D                | 00*1       | 00                 | 1              | 1 |

| $\mathrm{B}_2$   | 001*       | 00                 | _              | 2 |

| D                | 110*       | 01                 | _              | 3 |

| $\mathrm{B}_4$   | 11*1       | U1                 | -              | 4 |

| $\mathrm{B}_{7}$ | 100*       | 10                 | $\mathbf{z}_1$ | 5 |

| $\mathbf{D}_7$   | 10*1       | 10                 | $\mathbf{z}_1$ | 6 |

Из табл. 3 имеем систему (9):  $z_1 = \tau_1 \overline{\tau_2} \overline{\tau_3} \vee \tau_1 \overline{\tau_2} \tau_4$ . Отметим, что для подхода, предложенного в [10], БПК должен реализовать и уравнение  $z_2 = \tau_1 \overline{\tau_2} \overline{\tau_3} \vee \tau_1 \overline{\tau_2} \tau_4$ .

При реализации блока УП имеются следующие особенности. Часть кода  $K(B_i)$ , определяемая множеством  $Z^2$ , помещается в ячейки УП, адреса которых соответствуют выходам ОЛЦ. Этот этап выполняется тривиальным образом и в данной статье не рассматривается.

#### Выводы.

Предлагаемый в работе метод оптимизации КМУУ основан на мультиплексировании трех источников кодов классов псевдоэквивалентных ЭОЛЦ. Такой подход позволяет гарантированно уменьшить число термов в системе функций возбуждения триггеров регистра и счетчика адресов микрокоманд до максимально возможной величины. Если КМУУ с элементарными цепями рассматривать как автомат Мура, то предлагаемый подход позволяет уменьшить число термов до величины этого параметра у эквивалентного автомата Мили. Кроме того, уменьшается число LUT-элементов в схеме преобразователя кодов, так как не все адреса выходов ЭОЛЦ подлежат преобразованию и не все разряды кодов классов формируются.

Недостатком предложенного подхода является введение мультиплексора, который вносит дополнительную задержку в цикл работы КМУУ. Однако уменьшение числа термов ведёт к уменьшению числа уровней в схеме и задержка от введения МИК компенсируется. Проведенные авторами исследования показали, что предложенный метод позволяет до 42% уменьшить число LUT-элементов по отношению к исходному КМУУ. При этом время цикла КМУУ  $U_2$  всегда было меньше, чем у КМУУ  $U_1$ .

Научная новизна предложенного метода заключается в использовании особенностей КМУУ (наличие классов псевдоэквивалентных ЭОЛЦ) для уменьшения числа LUТ-элементов в схеме КМУУ с элементарными цепями.

Практическая значимость метода заключается в уменьшении площади кристалла FPGA, занимаемой схемой КМУУ, что позволяет получить схемы, обладающие меньшей стоимостью, чем известные из литературы аналоги.

#### Список использованной литературы

- 1. Barkalov A., Titarenko L. Logic synthesis for compositional microprogram control units. Berlin: Springer, 2008. –272 pp.

- 2. Баркалов А.А., Титаренко Л.А. Синтез микропрограммных автоматов на заказных и про-

- граммируемых СБИС. Донецк: УНИТЕХ, 2009.–336 с.

- 3. Barkalov A., Titarenko L. Logic synthesis for FSM-based control units. Berlin: Springer, 2009. –233 pp.

- 4. Maxfield S. The Design Warrior's Guide to FPGAs. Amsterdam: Elsevier, 2004. 541 pp.

- 5. Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем на микросхемах с программируемой структурой С-Пб: БХВ Петербург, 2006. 736 с.

- 6. xilinx.com.

- 7. altera.com.

- 8. Baranov S. Logic and System Design of Digital Systems. Tallinn: TTU, 2008. 266 pp.

- 9. Баркалов А,А, Титаренко Л.А., Ефименко К.Н., Липински Я.М. Оптимизация схемы КМУУ с преобразователем адреса микрокоманд // Наукові праці ДонНТУ. Серія "Проблеми моделювання та автоматизації проектування" (МАП-2011). Випуск 9 (179). Донецьк: ДонНТУ. 2011. С.26-35.

- 10. Баркалов А,А, Титаренко Л.А., Ефименко К.Н., Липински Я.М. Оптимизация схемы КМУУ с элементарными цепями // Наукові праці ДонНТУ. Серія "Проблеми моделювання та автоматизації проектування" (МАП-2011). Вип.10 (197). Донецьк: ДонНТУ. 2011. С.21-30.

Надійшла до редакції:

рецензент:

20.03.2013р.

д-р техн. наук, проф.

A.A. Barkalov, K.N. Efimenko, I.J. Zelenjova. Optimization of addressing circuit for CMCU with elementary chains. The article is devoted to development of methods of synthesis and optimization of compositional microprogram control units (CMCU) of FPGA (field-programmable logic arrays). For optimization of resources of a system-on-a-chip used at realization of the compositional microprogram control unit the method of a structural reduction. A method for reducing the hardware amount in the circuit of CMCU with elementary chains is proposed oriented on FPGA technology. The method is based on the use of three sources of codes classes of pseudoequivalent EOLC (elementary operational linear chains) and a multiplexer to choose one of these sources. Such an approach would reduce the number of LUT (look-up table)-elements in the addressing circuit of CMCU. Application of the specified method to the finite state machine of addressing CMCU, under its implementation with FPGA, leads to reduction of the number of LUT-elements in the circuit of the control unit. Results of research of the developed structures are resulted, allowing defining their efficiency and an area of optimum application. An example of the proposed method application is given.

**Keywords:** compositional microprogram control units, GSA, elementary operational linear chains, FPGA, logic circuit.

**О.О.** Баркалов, К.М. Ефіменко, І.Я. Зеленьова. Оптимізація схеми адресації КМПК із елементарними ланцюгами. В роботі запропоновано метод зменшення апаратурних витрат у схемі КМПК із елементарними ланцюгами, який орієнтовано на технологію FPGA. Метод засновано на використанні трьох джерел кодів класів псевдоеквівалентних ЕОЛЛ та мультіплексору, який дозволяє вибрати одне з цих джерел. Такій підхід дозволить зменшити число LUT елементів у схемі адресації КМПК. Наведено приклад використання запропонованого методу.

**Ключові слова:** композиційний мікропрограмний пристрій керування, ГСА, елементарний операторній лінійний ланцюг, FPGA, логічна схема