УДК 004.3

## Инкрементные алгоритмы решения систем линейных алгебраических уравнений и архитектура мультипроцессоров на программируемой логике

Гомозов О.В., Ладыженский Ю.В. Донецкий национальный технический университет blackswanny@gmail.com, ly@cs.dgtu.donetsk.ua

#### Abstract

Gomozov O., Layzhenskyy Y. Incremental algorithms of linear equations algebraic systems solving and multiprocessor architecture based on programmable logic. The method of solving linear equations systems by incremental algorithms is described. Simulation with different conditions is performed to see their behavior in hardware implementation of abstract model, comparisons between these algorithms and other iterative ones are made. FPGA hardware structures are proposed for implementation of these algorithms.

#### Введение

Во многих научно-технических сферах, инженерных задачах, гуманитарных и социальноориентированных науках часто используются СЛАУ (системы линейных алгебраических уравнений). Ими описываются математические модели, физические процессы, динамические системы и задачи. Получаемые системы могут включать сотни и тысячи уравнений. При этом возникает проблема скорости решения таких задач и корректности полученных результатов. Обе проблемы решаются с использованием машин. Существует вычислительных основных направления в решении СЛАУ: прямые и итерационные методы. Прямые методы находят решение за конечное число шагов, однако сложны в реализации и не всегда устойчивы. В итерационных методах для СЛАУ вида

$$A \cdot x = b, \tag{1}$$

где A — матрица коэффициентов, b — вектор свободных членов, x- вектор неизвестных, решение происходит путем вычисления последовательных приближений  $x^k$  при  $k \to \infty$ , где k - номер итерации. Условием окончания итерации является выполнение неравенства  $\|Ax^{(k)} - b\| \le eps$ , где eps – погрешность.

В данной статье исследуются свойства специальных аппаратно-ориентированных итерационных алгоритмов решения СЛАУ. Разработана архитектура мультипроцессора на программируемой логике для эффективной аппаратной реализации этих алгоритмов.

### Анализ инкрементных алгоритмов

СЛАУ приводим к эквивалентной системе линейных дифференциальных уравнений:

$$\frac{dx_i}{dt} = b_i - \sum_{i,j=1}^{n} a_{ij} x_i, i, j = 1,2...n, n - nopядок СЛАУ$$

Применяя метод Эйлера[1], получим обобщенные формулы для инкрементных алгоритмов:

$$x_i^{k+1} = x_i^k + \Delta x_i^{k+1};$$

$$\Delta x_i^{k+1} = 2^{-p} \cdot sign(\varepsilon_i^k),$$

$$\boldsymbol{\varepsilon}_{i}^{k+1} = \boldsymbol{\varepsilon}_{i}^{k} + \Delta \boldsymbol{\varepsilon}_{i}^{k+1};$$

$$\Delta \varepsilon_i^{k+1} = -\sum_{i=1}^n a_{ij} \Delta x_j^{k+1}, \quad \varepsilon \partial e \ x_j^0 = 0, \varepsilon_i^0 = b_i, \quad (2)$$

где  $a_{ii}$  – коэффициент матрицы A,

$b_i$  – свободный член,  $x_i$  – неизвестное,

$\Delta x_i$  – приращение неизвестного,

$\varepsilon_i$  – невязка,  $\Delta \varepsilon_i$  – приращение невязки,

i – номер неизвестного, k – номер итерации,

р – разрядность величин

Формулы (2) показывают, что инкрементные алгоритмы ориентированы на использование простых операций сложения, а трудоемкое умножение заменяется операцией сдвига, так как приращение  $\Delta x_i$  является степенью числа 2.

Невязка

$$\varepsilon_i(x) = b_i - \sum_{i=1}^n a_{ij} x_i$$

входит в

критерий сходимости [2]:

$$\sum_{i=1}^{n} (\varepsilon_i^k)^2 \le E \tag{3}$$

Вторым критерием окончания решения может быть ограничение на максимальное количество итераций. Псевдокод алгоритма (2) представлен на рис. 1.

BEGIN PROGRAM

$$k := 0$$

SET p,eps, Im

$FOR i := 1 TO N$

$\varepsilon_i := b_i$

$x_i := 0$

END FOR

REPEAT

$cr := 0$

$FOR i := 1 TO N$

$\Delta x_i := 2^{-p} \cdot sign(\varepsilon_i)$

$\Delta \varepsilon_i := 0$

$FOR j := 1 TO N$

$\Delta \varepsilon_i := \Delta \varepsilon_i + a_{ij} \Delta x_j$

END FOR

$\varepsilon_i := \varepsilon_i - \Delta \varepsilon_i$

$x_i := x_i + \Delta x_i$

$cr := cr + (\varepsilon_i)^2$

END FOR

$k := k + 1$

UNTIL  $(cr < eps) OR (k > Im)$

END PROGRAM

Рисунок 1 – Псевдокод обобщенного инкрементного алгоритма

Модификации основного алгоритма обеспечиваются различными вариантами формулы нахождения приращения неизвестного  $\Delta x_i^{k+1}$ . Существует 4 метода [2]:

$$\Delta x_i^{k+1} = 2^{-p} \cdot sign(\varepsilon_i^k) \tag{4}$$

Метод №2:

$$\Delta x^{k+1} = 2^{-r} \cdot sign(\varepsilon^k), \tag{5}$$

где

$$r = 1, 2... p - 1, p$$

Метод №3:

$$\Delta x^{k+1} = 2^{-\frac{p}{S}} \cdot sign(\varepsilon^k),$$

$$e\partial e \ S = r, \frac{r}{2}, \frac{r}{3}, \dots, 1,$$

(6)

В методе  $N \hspace{-0.05cm} \underline{\hspace{0.05cm} 3}$  каждые  $2^{\frac{P}{r}}$  итерации выбирается новое S(r- количество участков, на которые разбивается

разрядность р)

Метод №4:

$$\Delta x^{k+1} = 2^{-z} \cdot U_i \cdot sign(\varepsilon_i^k);$$

$$z = \min_{i=1..n} m_i; \quad 2^{-m_i} \le \varepsilon_i^k < 2^{-m_i+1};$$

$$U_i = \begin{cases} 1, \varepsilon_i^k \ge 2^{-z} \\ 0, \varepsilon_i^k < 2^{-z} \end{cases}$$

(7)

Количество итераций к для получения решения с заданной точностью зависит от разрядности данных. Для исследования описанных методов создана модель работы алгоритмов на языке программирования С для нескольких видов матриц, в частности диагональдоминирующих, трехдиагональных и матриц Гильберта[6]. В таб. 1 представлены результаты исследования сходимости методов для матрицы с доминирующей диагональю. В строках указан метод решения, в столбцах разрядность данных, в ячейках – количество итераций.

Таблица 1. Количество итераций в инкрементных

| методах    |             |                  |       |           |      |  |

|------------|-------------|------------------|-------|-----------|------|--|

|            | Разрядность |                  |       |           |      |  |

| Метод      | 16          | 24               | 32    | 48        | 64   |  |

| <b>№</b> 1 | 65536       | >10 <sup>6</sup> | >109  | >109      | >109 |  |

| №2         | 16          | 24               | 32    | 48        | 64   |  |

| №3         | 512         | 8192             | 65536 | $>10^{6}$ | >109 |  |

| <b>№</b> 4 | 64          | 128              | 256   | 512       | 1024 |  |

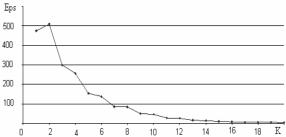

Как видно из табл.1, наиболее эффективными являются методы №2 и №4. Важно отметить, исходя из формул (1), возможности параллельного вычисления каждого неизвестного на каждой итерации. На рис.2 приведен график зависимости ошибки решения Ерѕ, равной сумме модулей невязок, от номера итерации К на примере матрицы Гильберта [6] размером 1000 уравнений. На итерациях второго порядка ошибка составляет менее 0,01 [3].

Рисунок 2 – Скорость сходимости методов

# VHDL моделирование инкрементных алгоритмов

Для исследования свойств алгоритмов разработана модель на языке VHDL в среде Active-HDL. Модель обрабатывает числа с фиксированной запятой. В качестве тестовых

использовались матрицы: Dom - матрицы с доминирующими элементами на главной диагонали и Gil - плохо обусловленные матрицы Гильберта, для которых многие итерационные алгоритмы расходятся или решения являются чувствительности ошибочными из-за погрешностям коэффициентов матрицы А. На рис. 3 - 6 представлены временные диаграммы решения системы с матрицей Dom, где: А матрица коэффициентов, В – вектор свободных членов, Хх - вектор найденных неизвестных, кколичество итераций, N - порядок СЛАУ, Р разрядность данных, Х - истинные значения неизвестных.

| Name 🛆  | Value                              | 360 3 380 ns          |

|---------|------------------------------------|-----------------------|

| ±⇔A     | (132,-80,51,-74,167,-94,46,86,146) |                       |

| ±⇔B     | (14501,-11204,16701)               |                       |

| V= k    | 94                                 | 3 \90 \91 \92 \93 \94 |

| ± V= Xx | (88,14,78)                         |                       |

Рисунок 3 – Моделирование N=3,P=16,Dom,X=88,14,78

| Name A     | Value                               | <u> </u> | 1  | 130                     | 1  |    | 140 | 1  | 15 |

|------------|-------------------------------------|----------|----|-------------------------|----|----|-----|----|----|

| ⊕⇔∆        | (103,-17,-88,25,107,-39,48,-93,140) |          |    |                         |    |    |     |    |    |

| <b>⊕</b> B | (760,3046,3028)                     |          |    |                         |    |    |     |    |    |

| V= k       | 37                                  | 30       | 31 | X32 X                   | 33 | 34 | 35  | 36 | X  |

| ⊕ V=×x     | (37,29,27)                          |          | X  | $\overline{\mathbb{X}}$ |    | Ĉ  | X   | χ  | X  |

Рисунок 4 – Моделирование N=3,P=32,Dom,X=36,30,29

| Name △ | Value                         | 300 314 ns                             |

|--------|-------------------------------|----------------------------------------|

| ⊕Α     | (100,50,33,50,33,25,33,25,20) | —————————————————————————————————————— |

| ⊕ B    | (12612,7193,5118)             |                                        |

| V= k   | 78                            | <sup>7</sup> 4 \75 \76 \77 \7          |

| ± V=×x | (76,58,56)                    |                                        |

Рисунок 5 – Моделирование N=3,P=48,Dom,X=77,58,56

| Name A     | Value                              | 380 1 390 404 ns   |

|------------|------------------------------------|--------------------|

| ⊕⇔A        | (164,-92,44,88,154,-67,75,-33,111) |                    |

| <b>⊕</b> B | (16395,8000,14413)                 |                    |

| V≕k        | 100                                | 95 96 97 98 99 100 |

| ± V=×x     | (96,28,72)                         |                    |

Рисунок 6 – Моделирование N=3,P=64,Dom,X=96,28,72

Как видно из рис. 3-6 VHDL-модель решает СЛАУ быстро и с погрешностью, не

превышающей младшего разряда, в том числе при малой разрядности данных. Однако в случае с матрицей Гильберта возрастает погрешность вычисления, связанная с ошибкой округления входных данных. Для противодействия этому эффекту возможно увеличение разрядности данных, результаты представлены на рис. 7 и рис.8.

| Name △     | Value                                  | 3268 ns      |

|------------|----------------------------------------|--------------|

| ⊕⇔Α        | (1000,500,333,500,333,250,333,250,200) |              |

| ⊕ <b>B</b> | (1261202,719341,511807)                |              |

| V= k       | 816                                    | ()()()()(81) |

| ⊕ V= Xx    | (808,570,500)                          | 0000         |

Рисунок 7 — Моделирование N=3,P=32,Gil,X = 809,585,480

| Name A       | Value                                       | 3640 ns |

|--------------|---------------------------------------------|---------|

| ⊕⇔A          | (1000,500,333,250,200,166,142,125,111,100,5 |         |

| ⊕ <b>⊕</b> B | (1638086,1213670,986158,837090,729950,64{   |         |

| V= k         | 909                                         | XXXX    |

| ± V=×x       | (223,743,901,899,772,618,533,443,547,664)   | M       |

Рисунок 8 — Моделирование N=10,P=64,Gil,X = 210,780,894,897,754,611,422,466,567,840

Модификации (5)-(7) алгоритма способны уменьшить количество итераций, и увеличить скорость сходимости алгоритма [3].

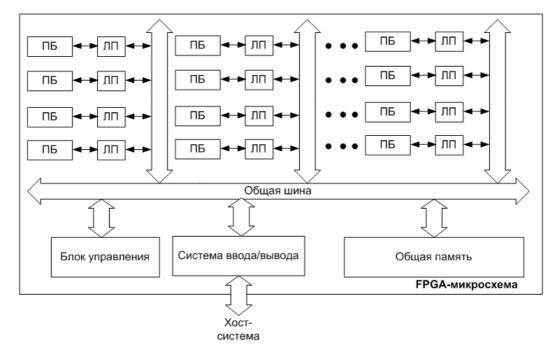

# **Архитектура мультипроцессора для** реализации инкрементных методов

аппаратной реализации вышеприведенных алгоритмов можно FPGA[4], использовать интегральные схемы выпускаемые фирмами Xilinx, Altera, Lattice и др. состав **FPGA** входят отдельные программируемые блоки памяти и шины данных. Такая структура дает возможность сконфигурировать запрограммировать И микросхемы, наиболее эффективно используя инкрементных достоинства алгоритмов, частности, распараллеливание вычислений [5]. Реализация на FPGA является расширяемым и масштабируемым решением. Микросхемы **FPGA** позволяют создавать многомодульные И многоядерные вычислительные системы всего на одном кристалле, сконфигурированные под целевые задачи.

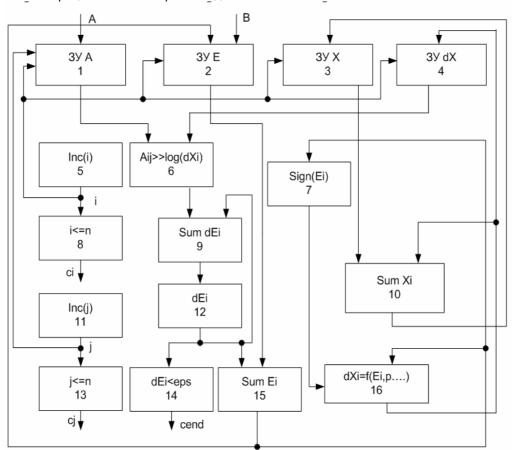

Обобщенная функциональная схема процессора, реализующего инкрементные методы, представлена на рис.9. Блоки 1,2,3 и 4 –

запоминающие устройства для хранения матрицы A, вектора невязок E, вектора неизвестных X и вектора приращений неизвестных dX соответственно. В начале работы в блоки 1 и 2 загружаются матрица A и вектор свободных

членов b. Блоки 5 и 8 реализуют адресацию строки в памяти 3У для текущего i-го уравнения. Аналогично реализуют адресацию блоки 11 и 13 для индекса столбца ј матрица A.

Рисунок 9 – Обобщенная структура процессора

Рисунок 10 – Структура мультипроцессора

Блок 6 производит операцию сдвига коэффициента  $a_{i,j}$  на количество разрядов, равное  $\log_2 dX_i$ , что равнозначно операции  $a_{i,j}*dX_i$ .

Блоки 9 и 12 — это сумматор и аккумулирующий регистр для вычисления значения приращения невязки  $dE_i$ . В блоке 14 проверяется условие конца решения, т.е. условие сходимости невязок к некоторой величине погрешности eps. В блоке 15 происходит вычисление текущей невязки по формуле  $E_i = E_i - dE_i$ .

Знак невязки, полученный в блоке 7, используется в блоке 16 для выполнения одного из алгоритмов нахождения приращения неизвестного, в каждом из которых участвует операция сдвига невязки. Последняя операция нахождения неизвестного происходит в блоке 10 по формуле  $x_i = x_i + dx_i$ .

В данной структуре самыми ресурсоемкими являются блоки суммирования, а все операции умножения заменены простыми и быстрыми операциями сдвига. Также возможны другие модификации, например, использование одного сумматора, мультиплексора данных и группы накапливающих регистров вместо трех сумматоров, приведенных на рис. 9.

Процессоры, описанные на рис. 9, могут объединяться в многопроцессорные схемы, как показано на рис. 10. Каждый из них представляет собой процессорный блок (ПБ) со своей локальной памятью (ЛП), работающий параллельно с остальными. Перед началом работы в общую память загружаются исходные данные (матрица коэффициентов, вектор свободных членов, параметры) через систему ввода/вывода, связывающую устройство с внешней хостсистемой. Блок управления проверяет условие решения после каждой итерации, посылает управляющие сигналы. Для быстрого доступа локальная память процессорного блока кеширует данные, которые загружаются в неё из общей памяти. Каждый ПБ может произвести итерацию для одного уравнения СЛАУ. Если количество ПБ меньше количества уравнений, блок управления формирует очередь (конвейер) этих уравнений, отдавая данные свободным ПБ до тех пор, пока в текущей итерации не будут вычислены все. При этом скорость решения будет уменьшаться пропорционально отношению количества уравнений к количеству ПБ.

Рассматриваемые мультипроцессорные схемы могут быть реализованы на FPGA, так как они позволяют создание таких архитектур. При параллельной реализации условное количество вентилей на один процессорный блок с локальной памятью равно:

$$C = 3Y_A + 3Y_E + 3Y_X + 3Y_{dX} + 3*SUM + 2*SREG + 2*CS$$

(8)

,где  $3V_A$ ,  $3V_E$ ,  $3V_X$  и  $3V_{dX}$  - запоминающие устройства (1 вентиль на бит) соответствующих данных, SUM — сумматор (9 вентилей на бит), SREG — сдвиговый регистр (3 вентиля на бит), CS — схема сравнения (2 вентиля на бит). При разрядности данных M=32 бита и размере СЛАУ N=100 уравнений

$$C = 100 * 32 + 32 + 32 + 32 + 3 * 32 * 9 + 2 * 32 * 3 + 2 * 2 * 32 = 1600$$

из которых 1184 вентиля используются для процессорного блока и 416 вентилей - для локальной памяти.

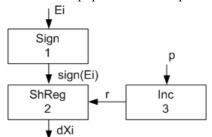

Реализация блока приращения 16 зависит от выбранного инкрементного алгоритма. Возможны следующие схемы, представленные на рис. 11-14:

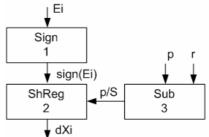

Рисунок 11 – Блок приращения в алгоритме 1

Рисунок 12 – Блок приращения в алгоритме 2

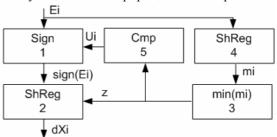

Рисунок 13 – Блок приращения в алгоритме 3

Рисунок 14 – Блок приращения в алгоритме 4

Блоки 1 и 2 на рис. 11-14 одинаковы для всех алгоритмов и реализуют соответственно схему анализа знака и сдвиговый регистр. Блок 3 на рис. 12 является инкрементором для нахождения г, а на рис. 13 вычитателем для нахождения величины р/S. На рис.14 блоки 3 (схема сравнения) и 4 (сдвиговый регистр) вычисляют значение z, необходимое для схемы сравнения (блок 5).

#### Выводы

Проведены исследования итерационных инкрементных алгоритмов решения СЛАУ, изучены их свойства и особенности. С применением моделирования получены различные характеристики алгоритмов: скорость сходимости, устойчивость к видам и разрядности данных. Предложены варианты аппаратной реализации алгоритмов на FPGA с использованием параллельных вычислений.

Показано, что инкрементные методы обладают важными для практического применения свойствами:

- высокая скорость решения задач и простота арифметических операций;

- устойчивость и отсутствие ограничений для многих классов задач;

- возможность эффективной реализации на базе микросхем FPGA.

### Литература

- 1. Малиновский Б.Н., Боюн В.П., Козлов Л.Г. Алгоритмы решения систем линейных алгебраических уравнений, ориентированные на структурную реализацию. "Управляющие системы и машины". Вып. №5. 1977, с.79-84.

- 2. Боюн В.П., Козлов Л.Г., Малиновский Б.Н., Третьяков С.И. Устройства для решения систем линейных алгебраических уравнений. Автор. свид. № 543943 БИ, 1977, № 3.

- 3. Куркчи В.А., Гомозов О.В., Ладыженский Ю.В. Исследование инкрементных методов решения СЛАУ. Донецк, ДонНТУ: Всеукраинская научно-техническая конференция "КМиТ", 2009, с. 190-193.

- 4. Hongyan Yang, Sotirios G. Ziavras. FPGA-based Vector Processor for Algebraic Equation Solvers. http://web.njit.edu/~ziavras/Wmatrix.pdf

- 5. Максфилд К. Проектирование на ПЛИС. М.: "Додека-XXI", 2007, 408с.

- 6. Ланкастер П. Теория матриц. М.:"Наука", 1973, 282с.

# Приложение. Матрицы для экспериментов

Для исследования свойств инкрементных методов и проведения моделирования были выбраны виды матриц, имеющие свои особенности и область использования, покрывающие наиболее известные классы задач по различным критериям.

**Диагональ-доминирующая** матрица подчиняется условию:

$$a_{i,i} \ge \sum_{j=1}^{n} |a_{i,j}|, \ \partial e \ i \ne j; i, j = 1..n$$

(8)

т.е. элемент главной диагонали больше либо равен сумме модулей остальных элементов строки. Такая матрица часто встречается, и известные итерационные методы для нее сходятся.

В сеточных задачах математической физики, при расчете электрических цепей и во многих областях используются ленточные матрицы. Частным случаем ленточной является *только матрица.* У неё ненулевые элементы содержатся только на главной диагонали, а также смежными с ней нижней и верхней диагоналями, т.е.:

$$a_{i,i} \ge 0, a_{i,j-1} \ge 0, a_{i,j+1} \ge 0, \partial e \ i, j = 1..n \ (9)$$

Наибольший интерес представляет матрица Гильберта. Она является плохо обусловленной, почти вырожденной матрицей, т.е. её определитель близок к нулю. Один из примеров матрицы Гильберта определяется следующей формулой:

$$a_{i,i} = \frac{1}{i+j-1}$$

,  $z \partial e \ i, j = 1..n$  (10)

Такие СЛАУ чувствительные к точности коэффициентов матрицы, что показывает число обусловленности. Из-за этого при решении многими методами возникают ложные корни, что особенно актуально при ошибках округления, возникающих в вычислительных устройствах.

Поступила в редакцию 15.03.10