# Розділ 3. Інформаційно-вимірювальні системи, електронні та мікропроцесорні прилади

УДК 004.274

## А.А. Баркалов, С.А. Цололо, Х. Байрак

Университет Зеленогурский, г. Зелёна Гура, Польша Донецкий национальный технический университет, г. Донецк, Украина A.Barkalov@iie.uz.zgora.pl

# МАТРИЧНАЯ РЕАЛИЗАЦИЯ КОМПОЗИЦИОННОГО МИКРОПРОГРАММНОГО УСТРОЙСТВА УПРАВЛЕНИЯ С РАЗДЕЛЕНИЕМ КОДОВ

#### Аннотация

Баркалов А.А., Цололо С.А., Байрак Х. Матричная реализация композиционного микропрограммного устройства управления с разделением кодов. В работе предложена модель композиционного микропрограммного устройства управления с разделением кодов. Предложенный метод основывается на представлении адреса вершины алгоритма управления в виде конкатенации кодов ОЛЦ и кода компоненты ОЛЦ. Такой подход уменьшает число входов и выходов схемы формирования функций возбуждения, что позволяет снизить аппаратурные затраты в логической схеме КМУУ.

**Ключевые слова:** устройство управления, матричная реализация, КМУУ, разделение кодов, заказная матрица.

### Введение.

Одним из методов реализации устройства управления цифровой системы является использование модели композиционного микропрограммного устройства управления (КМУУ) [1,2]. Эти устройства идеально подходят для реализации с использованием современных СБИС типа FPGA [3], где имеются средства для реализации произвольной логики и встроенные блоки памяти [4, 5]. В тоже время при массовом производстве изделий электронной промышленности по-прежнему широко используются заказные схемы типа ASIC (Application Specific Integrated Circuits) [6]. В этом случае для реализации схем устройств управления используются заказные матрицы [7], основанные на распределенной логике [8]. В настояще время в литературе практически отсутствуют методы, ориентированные на этот базис. В настоящей статье рассматривается метод синтеза КМУУ с разделением кодов на заказных матрицах, и анализируются пути уменьшения площади кристалла, занимаемой его логической схемой.

Целью исследования является реализация логической схемы устройства управления на заказных СБИС при интерпретации линейного алгоритма управления. Задачей исследования является разработка метода синтеза КМУУ с разделением кодов, позволящего уменьшить площадь заказных матриц в его логической схеме. При этом алгоритм управления представляется в виде граф-схемы алгоритма (ГСА) [7].

#### Основные определения и общие положения.

Пусть исходная ГСА  $\Gamma$  имеет начальную вершину  $b_0$ , конечную вершину  $b_E$ , операторные вершены из множества  $B_1$  и условные вершины из множества  $B_2$ . В вершинах  $b_q \in B_1$  записываются микрокоманды  $Y(b_q) \subseteq Y$ , где  $Y = \{y_1,...,y_N\}$  — множество микроопераций. В вершинах  $b_q \in B_2$  записаны элементы множества логических условий

$X = \{x_1, ..., x_2\}$ . Вершины ГСА Г связаны дугами  $\{x_1, x_2\}$ , образующими множество дуг Е. Введем ряд определений [1,2], необходимых для дальнейшего изложения материала.

Определение 1. операторной линей целью (ОЛЦ) ГСА  $\Gamma$  называется конечная последовательность операторных вершин  $\alpha_g = < b_{g_1},...,b_{g_{f_g}}>$ , такая, что для любой пары соседних компонент вектора  $\alpha_g$  существует дуга  $< b_{g_i}, b_{g_{i+1}}> \in E$ .

Произвольная ОЛЦ  $\alpha_g$  может иметь более одного входа, обозначим j-й вход ОЛЦ  $\alpha_g$  как  $I_g^j$ . Каждая ОЛЦ имеет только один выход  $O_g$ , входящий в множество  $O(\Gamma)$  выходов ОЛЦ ГСА  $\Gamma$ .

Пусть для ГСА  $\Gamma$  сформировано множество ОЛЦ С= $\{\alpha_1, \dots \alpha_G\}$ , удовлетворяющее условию

$$D^{i} \cap D^{j} = 0 \ (i \neq j; i, j \in \{1, ...G\});$$

$$D^{1} \cup D^{2} \cup ...D^{G} = B_{1};$$

(1)

При выполнении условия (1) каждая вершина  $b_q \in B_1$  входит точно в одну ОЛЦ  $\alpha_g \in C$ , число которых минимально. Пусть  $A(b_q)$ -двоичный адрес, соответствующий вершине  $b_q \in B_1$  и имеющий

$$R_{A} = \lceil \log_2 M \rceil \tag{2}$$

разрядов, где  $M = \left| B_1 \right|$ . Поставим в соответствие ОЛЦ  $\alpha_g \in C$  код  $K(\alpha_g)$  разрядности  $R_G$ , где

$$R_{G} = \lceil \log_{2} G \rceil \tag{3}$$

Пусть  $M_0 = \max(F_1,...,F_G)$ , поставим в соответствие каждой компоненте  $b_q \in D^g$  двоичный код  $K(b_q)$  разрядности  $R_C$ , где

$$R_{C} = \lceil \log_2 M_0 \rceil \tag{4}$$

При этом компоненты разных ОЛЦ  $\alpha_{\rm g} \in C$  имеют одинаковые коды. Выполним кодирование компонент так, чтобы выполнилось условие

$$K(b_{gi+1}) = K(b_{gi}) + 1,$$

(5)

где  $i=1,\ldots,F_g-1,g\in\{1,\ldots,G\}$ . Теперь внутри каждой ОЛЦ  $\alpha_g\in C$  код любой компоненты на единицу больше кода предыдущей компоненты. Используем для кодирования ОЛЦ переменные  $\tau_r\in \tau$ , где  $|\tau|=R_G$ , а для кодирования компонент — переменные  $T_r\in T$ , где  $M=R_C$ . Пусть для ГСА  $\Gamma$  выполняется условие

$$R_G + R_C = R_A. (6)$$

Назовем ГСА Г линейной ГСА, если выполняется условие

$$\frac{M}{G} \ge 2$$

, (7)

то есть если число ОЛЦ ГСА  $\Gamma$  хотя бы в два раза меньше числа ее операторных вершин. Если для линейной ГСА  $\Gamma$  выполняется условие (6), то для ее интерпретации целесообразно использовать модель КМУУ с разделением кодов (2), представленную на рис. 1. В дальнейшем эта модель обозначается символом  $U_1$ .

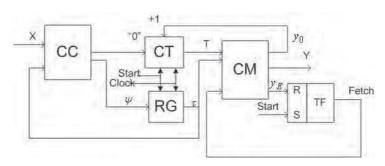

Рисунок 1 – Структурная схема КМУУ с разделением кодов

Здесь комбинационная схема СС реализует систему функций возбуждения счетчика СТ

$$\Phi = \Phi(\tau, X) \tag{8}$$

и систему функций возбуждения регистра RG

$$\Psi = \Psi(\tau, X). \tag{9}$$

Управляющая память СМ хранит микрооперации Y, сигнал управления синхронизацией  $y_0$  и сигнал управления выборкой из управляющей памяти  $y_E$ .

Устройство управления  $U_1$  функционирует следующим образом. По сигналу Start=1 в счетчик СТ и регистр RG заносятся нулевые коды, что соответствует адресу  $A(b_q)$ , где  $< b_0, b_q > \in E$ , одновременно триггер TF устанавливается в единичное состояние и сигнал Fetch разрешает выборку микрокоманд из СМ. Очередная микрокоманда  $Y(b_q)$  считывается из СМ. Если  $b_q \neq O_g$  ( $g=\overline{1,G}$ ), то одновременно с микрооперациями Y формируется сигнал  $y_0$ . При  $y_0=1$  по сигналу Clock к содержимому СТ прибавляется единица. Если  $b_q=O_g$  ( $g=\overline{1,G}$ ), то сигнал  $y_0$  не формируется и по сигналу Clock в RG заносится код очередной ОЛЦ, определяемый функциями  $\Psi$ , а в СТ заносится код компоненты, определяемый функциями  $\Phi$ . Если  $< b_q, b_E > \in E$ , где  $b_E$  — конечная вершина ГСА  $\Gamma$ , то формируется переменная  $y_E=1$ , триггер TF переходит в нулевое состояние и функционирование КМУУ прекращается. Отметим, что для КМУУ  $U_1$  адрес  $A(b_q)$  представляется в виде

$$A(b_q) = K(\alpha_g) * K(b_q), \qquad (10)$$

где  $\alpha_g \in C$ ,  $b_q \in D^g$ , «\*» — знак конкатенации. Такое представление адреса и называется разделением кодов [2].

Очевидно, КМУУ  $U_1$  является автоматом Мура, так как его выходные сигналы Y зависят только от внутренних переменных, входящих в множества  $\tau$  и T. При этом код ОЛЦ может рассматриваться как код состояния автомата. Однако в отличие от классического автомата Мура в схему КМУУ входит счетчик СТ, что вызывает отличие в методах синтеза.

#### Матричная реализация КМУУ с разделением кодов.

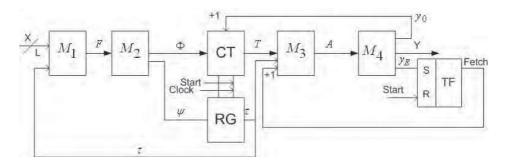

При реализации схемы КМУУ  $U_1$  на заказных матрицах, предлагаемой в данной работе, схема СС представляется в виде конъюнктивной матрицы  $M_1$  и дизъюнктивной

матрицы  $M_2$ . управляющая память СМ представляется в виде конъюнктивной матрицы  $M_3$  и дизъюнктивной матрицы  $M_4$  (рис. 2).

Рисунок 2 – Матричная реализация КМУУ с разделением кодов

В этой схеме матрица  $M_1$  реализует систему термов  $F = \{F_1,...,F_H\}$ , соответствующих строкам таблицы переходов КМУУ. При этом терм  $F_h \in F$  представляется в виде:

$$F_{h} = (\bigcap_{r=1}^{R_{G}} \tau_{r}^{l_{gr}}) \cdot X_{h}(h = 1, ..., H)$$

(11)

Первый член в формуле (11) соответствует коду  $K(\alpha_g)$  ОЛЦ  $\alpha_g \in C$ , переход из которой рассматривается в виде h-й строке таблицы. При этом  $1_{gr} \in \{0,1,^*\}$  — значение r-го разряда кода  $K(\alpha_g)$ ,  $\tau_r^0 = \overline{\tau_r}$ ,  $\tau_r^1 = \tau_r$ ,  $\tau_r^* = 1$ , где  $r \in \{1,...,R_G\}$ , а знак «\*» соответствует неопределенному значению разряда. Второй член формуле (11) соответствует входному сигналу, определяющему h-й переход и равному конъюкции некоторых элементов множества X (или их отрицаний). Матрица  $M_2$  формирует функции  $D_r \in \Phi \cup \Psi$ , представленные в виде дизъюнкции от термов (11):

$$D_{r} = \bigvee_{h=1}^{H} C_{rh} F_{h} (r = 1, ..., R_{G} + R_{C})$$

(12)

В (12) булева переменная  $C_{rh}=1$ , если и только если в h-й строке таблицы переходов  $D_r=1$  (h=1,...,H). отметим, что регистр RG и счетчик CT имеют информационные входы D-типа. Матрица  $M_3$  формирует термы  $A_m \in A$ , соответствующие адресам микрокоманд (10):

$$A_{m} = (\bigvee_{r=1}^{RG} \tau_{r}^{lgr}) \cdot (\bigvee_{r=1}^{RC} T_{r}^{lmr}) \cdot y_{E}$$

$$(13)$$

В выражении (13) второй член соответствует коду  $K(b_m)$  некоторой компоненты ОЛЦ  $\alpha_g \in C$ . При этом  $1_{mr} \in \{0,1,^*\}$  – значение r-го разряда кода  $K(b_m)$ ,  $T_r^0 = \overline{T_r}$ ,  $T_r^1 = T_r$ ,  $T_r^* = 1$ , где  $m \in \{1,...,M\}$ . Матрица  $M_4$  формирует функции  $y_0$ ,  $y_E$  И  $y_n \in Y$ , зависящие от термов (13):

$$y_{i} = \bigvee_{m=1}^{M} C_{im} A_{m}$$

(14)

где булева переменная  $C_{im} = 1$ , если и только если по адресу  $K(b_m)$  записана переменная  $y_i$   $(i \in \{0, E, 1, ..., N\})$ .

В настоящей работе предлагается метод матричной реализации КМУУ  $U_1$ , включающий следующие этапы:

- 1. <u>Формирование множества ОЛЦ С</u>. Этот этап выполняется по известной методике [1,2].

- 2. Кодирование ОЛЦ и их компонент. Этот этап, как и весь дальнейший синтез, выполняется только при соблюдении условий (6) и (7). При этом ОЛЦ  $\alpha_{\rm g} \in {\rm C}$  кодируются произвольным образом, а первые компоненты всех ОЛЦ получают нулевой код разрядности (4). Далее кодирование происходит так, чтобы выполнилось условие (5).

- 3. <u>Формирование системы формулы перехода</u>. Эта система (7) формируется для выходов ОЛЦ  $\alpha_{\rm g}\in C_1$ , где  $\alpha_{\rm g}\not\in C_1$ , если её выход связан с конечной вершиной ГСА  $\Gamma$ . Система формул перехода содержит  $G_1=\left|C_1\right|$  формулы, каждая из которых имеет следующий вид

4.

$$O_g \to \bigcup_{m=1}^{M} C_{gibi} \cdot X_{gi} \quad (g = 1, ..., G).$$

(15)

В формуле (15) булевая переменная  $C_{gi}=1$ , если и только если существует переход из вершины  $b_q=O_g$  в вершину  $b_i\in I(r)$ ;  $X_{gi}$  — конъюнкция некоторых элементов (или их отрицание)  $x_e\in X$ , определяющая переход из  $b_q=O_g$  в  $b_i\in I(r)$ , в системе (15) равняется числу строк таблицы переходов, а  $X_{gi}=X_h$  для терма номер h.

- 5. Формирование таблицы переходов КМУУ. Эта таблица строится по системе (15) и имеет столбцы:  $\alpha_{\rm g}$ ,  $K(\alpha_{\rm g})$ ,  $b_{\rm i}$ ,  $A(b_{\rm i})$ ,  $X_{\rm h}$ ,  $\Psi_{\rm h}$ ,  $\Phi_{\rm h}$ , h. Здесь  $\Psi_{\rm h}(\Phi_{\rm h})$  набор функций возбуждения, формирующий в СТ(RG) код компоненты (ОЛЦ) для h-го перехода КМУУ. Строки этой таблицы соответствуют термам (11), а функции  $D_{\rm r} \in \Phi \cup \Psi$  представляются в виде (12).

- 6. Формирование содержимого управляющей памяти. Эта таблица имеет столбцы  $b_q, A(b_q), y_0, y_E, Y(b_q)$  .q, где  $q \in \{1,...,M\}$  .Если  $b_q \neq O_g$  столбец  $y_0 = 1$  для адреса  $A(b_q)$ . Если  $< b_q, b_E > \in E$ , то столбец  $y_E = 1$  для адреса  $A(b_q)$ . Эта таблица является основной для формирования термов (13) и функций (14).

- 7. Реализация схемы КМУУ. Матрица  $M_2$  реализует термы (11), матрица  $M_2$  функции (12) , матрица  $M_3$  термы (13) , матрица  $M_4$  функции (14). Соединение этих матриц и счетчика СТ дает схему КМУУ  $U_1$ . Сложность каждой из матриц определяется ее площадью в условных единицах:  $S(M_j) = S_j * t_j$ ,где  $S_j$  количество входов и  $t_j$  количество выходов матрицы  $M_j$  (j=1,...,4).

#### Заключение.

Предложенный метод матричной реализации КМУУ с разделением кодов позволяет получить схему, соответствующую тривиальной реализации микропрограммного автомата. Для оптимизации этой схемы можно использовать как известные методы замены логических условий и кодирования наборов микроопераций [7], так и адаптировать методы оптимизации КМУУ, ориентированные на базис FPGA [2].

Научная новизна работы заключается в предложенных структуре и методе синтеза КМУУ с разделением кодов на заказных матрицах. Практическая значимость предложенного метода заключается в уменьшении площади кристалла, занимаемой схемой устройства управления, по сравнению с матричной схемой автомата Мура на основе регистра, хранящего коды состояний.

Дальнейшее направление исследований связано с адаптацией методов оптимизации схем КМУУ на стандартных СБИС к особенностям матричных схем.

#### Литература

- 1. Barkalov A.A., Titarenko L.A. Synthesis of operational and control automata. Donetsk: DonNTU, TechPark DonNTU UNITECH, 2009. 256 pp.

- 2. Баркалов А.А. Микропрограммное устройство управления как композиция автоматов с программируемой и жесткой логикой / А.А. Баркалов // Автоматика и вычислительная техника. -1983. N24. C. 36-41.

- 3. Максфилд К. Проектирование на ПЛИС. Курс молодого бойца / К. Максфилд. М.: Издательский дом «Додэка-XXI», 2007. 408 с.

- 4. Грушвицкий Р.И. Проектирование систем на микросхемах программируемой логики / Р.И. Грушвицкий, А.Х. Мурсаев, Е.П. Угрюмов. СПб.: БХВ-Петербург, 2002.-608 с

- 5. Соловьев В.В. Проектирование цифровых систем на основе программируемых логических интегральных схем / В.В. Соловьев. М.: Горячая линия Телеком, 2001. 636 с

- 6. Smith M. Application-Specific Integrated Circuits. Boston: Addison Wesley, 1997. 836 pp.

- 7. Баркалов А.А. Синтез микропрограммных автоматов на заказных и программируемых СБИС / А.А. Баркалов, Л.А. Титаренко. Донецк: ДонНТУ, Технопарк ДонНТУ УНИТЕХ,  $2009.-336~\rm c.$

- 8. Баранов С.И. Синтез микропрограммных автоматов / С.И. Баранов. Л.: Энергия, 1979.-236 с.

Надійшла до редакції: 31.01.2011

Рекомендовано до друку: д-р техн.наук, проф. Святний В.А.

#### Abstract

Barkalov A.A., Tsololo S.A., Biayrek H. Matrix realization of compositional microprogram control unit with code sharing. The structures of compositional microprogram control unit with code sharing are proposed. Structures allow reducing the complexity of the matrix realization in the device's circuit. The proposed method is based on using two codes sources. Described theoretical background and practical approach of synthesis; example of method application is given.

Keywords: CMCU, OLC, shared memory, matrix realization, gate array.

# Анотація

Баркалов О.О., Цололо С.О., Байрак X. Матрична реализація композиційного мікропрограмного пристрою керування із розділенням кодів. У роботі запропоновано модель композиційного мікропрограмного пристрою керування з розділенням кодів. Запропонований метод грунтується на представленні адреси вершини алгоритму управління у вигляді конкатенації кодів ОЛЛ та коду компоненти ОЛЛ. Такий підхід зменшує число входів і виходів схеми формування функцій збудження, що дозволяє знизити апаратурні витрати в логічній схемі КМПК.

**Ключові слова:** пристрій керування, матрична реалізація, КМПК, поділ кодів.

© Баркалов А.А., Цололо С.А., Байрак Х., 2011