# **А.А. Баркалов** (д-р техн.наук, проф.), **И.Я. Зеленёва** (канд.техн.наук, доц.),

**С.А. Цололо** (канд.техн.наук, доц.) **Х. Байрак** (аспирант) Донецкий национальный технический университет A.Barkalov@iie.uz.zgora.pl

# РАЗДЕЛЕНИЕ МАТРИЦЫ ТЕРМОВ ПРИ РЕАЛИЗАЦИИ СХЕМЫ КОМПОЗИЦИОННОГО МИКРОПРОГРАММНОГО УСТРОЙСТВА УПРАВЛЕНИЯ С ОБЩЕЙ ПАМЯТЬЮ

В работе предложены структуры композиционного микропрограммного устройства управления с общей памятью, позволяющие уменьшить сложность матричной реализации схемы устройства. Предложенный метод основывается на использовании двух источников кодов классов псевдоэквивалентных ОЛЦ, что приводит к разбиению матрицы термов в схеме адресации микрокоманд на две части.

КМУУ, ОЛЦ, общая память, матричная реализация, заказная матрица

### Введение

При массовом производстве средств вычислительной техники широко используются заказные матрицы [1]. Широко применяется этот базис и при реализации схем устройств управления (УУ) [2]. Если управляющий алгоритм представляет собой линейную граф-схему алгоритма (ГСА), то для реализации УУ может быть использована модель композиционного микропрограммного устройства управления (КМУУ) с общей памятью [3]. Подобное КМУУ представляет собой автомат Мура, в котором память состояний реализована на счетчике. При этом аналогом состояния автомата Мура для КМУУ является операторная линейная цепь (ОЛЦ) [4]. При реализации схем на заказных матрицах большое значение придается минимизации площади кристалла, занимаемого схемой [5]. В настоящей работе предлагается метод решения этой задачи, ориентированный на КМУУ с общей памятью.

*Целью исследования* является уменьшение площади, занимаемой схемой КМУУ с общей памятью за счет использования двух источников классов псевдоэквивалентных ОЛЦ и разделения матриц термов на две подматрицы.

Задачей исследования является разработка метода, позволяющего уменьшить аппаратурные затраты в схеме адресации микрокоманд КМУУ с общей памятью.

Для задания алгоритма управления, по которому строится схема КМУУ, используется язык ГСА [2].

## Реализация КМУУ с общей памятью на заказных матрицах

Пусть ГСА Г представлена множествами вершин В и дуг Е, соединяющих эти вершины. При этом  $B = \{b_0, b_E\} \cup E_1 \cup E_2$ , где  $b_0$  — начальная вершина ГСА,  $b_E$  — конечная вершина ГСА,  $E_1$  — множество операторных вершин, где  $|E_1| = M$ ,  $E_2$  — множество условных вершин. В вершинах  $b_q \in E_1$  записаны наборы микроопераций  $Y(b_q) \subseteq Y$ , где  $Y = \{y_1,...,y_N\}$  — множество микроопераций. В вершинах  $b_q \in E_2$  записаны элементы множества логических условий  $X = \{x_1,...,x_L\}$ . Пусть ГСА Г является линейной, то есть включает более 75% операторных вершин [3].

Сформируем множество ОЛЦ  $C = \{\alpha_1,...,\alpha_G\}$  ГСА  $\Gamma$ , где каждая из ОЛЦ является последовательностью операторных вершин и каждой паре её соседних компонент  $b_i, b_j$  соответствует дуга  $\langle b_i, b_j \rangle \in E$ . Каждая ОЛЦ имеет только один выход  $O_g$  и произвольное число входов  $I_g$  (g = 1,...,G). Формальные определения ОЛЦ, их входов и выходов можно найти в [3]. Каждая вершина  $b_q \in E_1$  соответствует микрокоманде  $MI_q$ , хранимой в управляющей памяти (УП) КМУУ по адресу  $A(b_q)$ . Для адресации микрокоманд достаточно

$$R = \lceil \log_2 M \rceil \tag{1}$$

бит, представленных переменными  $T_r \in T$ , где |T| = R. Пусть ОЛЦ  $\alpha_g \in C$  включает  $F_g$  компонент, а адресация микрокоманд выполнена так, что

$$A(b_{gi+1}) = A(b_{gi}) + 1,$$

(2)

где  $b_{gi} - i$ -я компонента ОЛЦ  $\alpha_g \in C \ (i = 1,...,F_g - 1)$ .

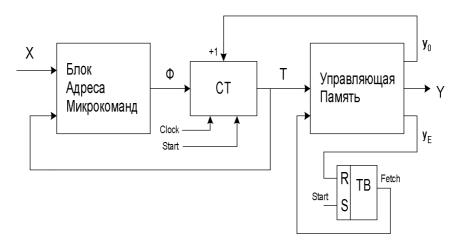

В этом случае для реализации схемы УУ можно использовать модель КМУУ с общей памятью (Рис. 1).

Рисунок 1 – Структурная схема КМУУ с общей памятью.

Условимся КМУУ, показанное на рис. 1, обозначать символом  $U_1$ . КМУУ  $U_1$  функционирует следующим образом.

По сигналу Start в счетчик (СТ) записывается начальный адрес микропрограммы, а триггер выборки (ТВ) устанавливается в единичное состояние. При этом  $\operatorname{Fetch}=1$ , что разрешает выборку микрокоманд из УП. Если считанная микрокоманда  $\operatorname{MI}_q$  не соответствует выходу ОЛЦ  $\alpha_g \in C_1$ , то одновременно с микрооперациями  $\operatorname{Y}(b_q)$  формируется переменная  $\operatorname{y}_0=1$ , что приводит к увеличению содержимого СТ на 1 (выражение (2), безусловный переход в пределах ОЛЦ). В противном случае  $\operatorname{y}_0=0$  и блок адресации микрокоманд формирует функции

$$\Phi = \Phi(T, X) \tag{3}$$

для записи в CT адреса микрокоманды перехода. Если достигнут выход ОЛЦ, связанной с вершиной  $b_E$ , то формируется сигнал  $y_E$  =1, триггер TB обнуляется и выборка микрокоманд из УП прекращается.

При реализации КМУУ  $U_1$  на заказных матрицах блок адресации микрокоманд (БАМ) реализуется на матрицах  $M_1$  и  $M_2$ , а УП — на матрицах  $M_3$  и  $M_4$  [6]. Матрица  $M_1$  реализует термы  $F_h \in F$  системы (3), где

$$F_{h} = A_{m}X_{h}. (4)$$

В уравнении (4)  $A_m$  — конъюнкция переменных  $T_r \in T$ , соответствующая адресу выхода  $O_g$  ОЛЦ  $\alpha_g \in C_1$ , определяющего h-й переход КМУУ, (h=1,...,H<sub>1</sub>). Матрица  $M_2$  реализует функции системы (3), представленные в виде

$$D_{r} = \bigvee_{h=1}^{H_{1}} C_{rh} F_{h}, \qquad (5)$$

где  $C_{rh}$  — булева переменная, равная единице, если и только если функция  $D_r$  (r=1,...,R) формируется на h-м переходе КМУУ.

Управляющая память реализована на матрицах  $M_3$  и  $M_4$ , при этом матрица  $M_3$  реализует систему термов

$$A_{m} = \bigwedge_{r=1}^{R} T_{r}^{l_{mr}}, \qquad (6)$$

где  $T_r \in T$ ,  $l_{mr} \in \{0,1\}$  — значение r-го разряда адреса микрокоманды  $MI_m$  (m=1,...,M),  $T_r^0 = \overline{T_r}$ ,  $T_r^1 = T_r$ , (r=1,...,R). Матрица  $M_4$  реализует функции  $y_i \in Y \cup \{y_0,y_E\}$ , где

$$y_i = \bigwedge_{m=1}^{M} C_{im} A_m.$$

(7)

В уравнении (7)  $C_{im}$  — булева переменная, равная единице, если и только если функция  $y_i$  записана в микрокоманде  $MI_m$  (m=1,...,M).

Недостатком КМУУ  $U_1$  является значительное число переходов  $H_1$  [3], определяемое особенностями автомата Мура. Для уменьшения этого параметра до числа переходов  $H_0$  эквивалентного автомата Мили используются методы, основанные на наличии псевдоэквивалентных ОЛЦ [7, 8].

### Оптимизация схемы КМУУ с общей памятью

Если выходы  $O_i$ ,  $O_j$  соединены с входом одной и той же вершины ГСА  $\Gamma$ , то ОЛЦ  $\alpha_i, \alpha_j \in C$  являются псевдоэквивалентными ОЛЦ (ПОЛЦ) [2, 5]. Найдем разбиение  $\Pi_C = \{B_1,...,B_I\}$  множества  $C_1 \subseteq C$  на классы ПОЛЦ. При этом ОЛЦ  $\alpha_g \in C_1$ , если ее выход не связан с вершиной  $b_E$  ГСА, то есть  $\langle O_g, b_E \rangle \notin E$ . Выполним адресацию микрокоманд так, чтобы при соблюдении условия (2) максимально возможное число классов  $B_i \in \Pi_C$  представлялось одним интервалом R-мерного булева пространства. Назовем такую адресацию опптимальной, а соответствующее ей КМУУ обозначим символом  $U_2$ .

Схема КМУУ  $U_2$  совпадает со схемой КМУУ  $U_1$ , но число термов  $H_2$  в системе (4) уменьшается. При этом  $H_0 \le H_2 < H_1$ . Если параметр  $H_0$  не достигнут, то классы  $B_i \in \Pi_C$  кодируются комбинациями  $K(B_i)$  разрядности

$$R_1 = \lceil \log_2 I \rceil. \tag{8}$$

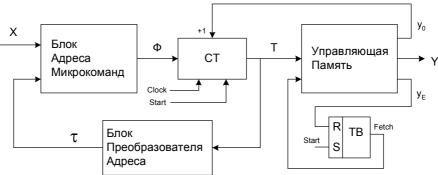

Используем для кодирования элементы множества  $\tau$ , где  $|\tau|=R_1$ . В этом случае для интерпретации ГСА  $\Gamma$  может быть использовано КМУУ с преобразователем адреса (рис. 2), обозначаемое в дальнейшем символом  $U_3$  [3].

Рисунок 2 — Структурная схема КМУУ  $U_3$  с преобразователем адреса

Устройство  $U_3$  функционирует аналогично КМУУ  $U_1$ , но блок БАМ реализует систему

$$\Phi = \Phi(\tau, X) \tag{9}$$

для записи в СТ адреса входа очередной ОЛЦ. При этом блок преобразователя адреса (БПА) формирует функции

$$\tau = \tau(T), \tag{10}$$

равные единице в коде  $K(B_i)$ , где  $\alpha_g \in B_i$ . Если достигнут выход ОЛЦ  $\alpha_g \notin C_1$ , то формируется  $y_E = 1$ , триггер TB обнуляется и выборка микрокоманд прекращается.

При реализации КМУУ  $U_3$  на заказных матрицах система (9) реализуется матрицей  $M_1$ . Термы указанной системы имеют вид

$$F_h = Q_i X_h, (11)$$

где  $Q_i$  — конъюнкция переменных  $\tau_r \in \tau$ , определяющая код класса  $B_i \in \Pi_C$ . Для реализации блока БПА используются матрицы  $M_5$  и  $M_6$ . Матрица  $M_5$  реализует термы вида (6), однако некоторые из функций  $l_{mr}$  могут быть неопределены, то есть обозначены \*. Итак,  $l_{mr} \in \{0,1,*\}$ ,  $T_r^0 = \overline{T_r}$ ,  $T_r^1 = T_r$  и  $T_r^* = 1$  (r = 1, ..., R). Матрица  $M_6$  реализует систему функций (10), представленную в виде

$$\tau_{\rm r} = \bigvee_{\rm m=1}^{\rm M} C_{\rm rm} A_{\rm m}, \qquad (12)$$

где  $C_{rm}$  — булева переменная, равная единице, если и только если переменная  $\tau_r$  =1 в коде класса  $B_i$   $\in$   $\Pi_C$ , включающего ОЛЦ с адресом выхода  $A_m$ .

При такой организации КМУУ число термов в системе (9) гарантированно равно  $H_0$  ( $H_3 = H_0$ ). Однако это достигается за счет введения блока БПА, который потребляет некоторые ресурсы кристалла. В настоящей работе предлагается метод реализации КМУУ, в котором число термов БАМ гарантированно равняется  $H_0$ , но площадь блока БПА уменьшается по сравнению с КМУУ  $U_3$ .

# **Разделение матрицы термов схемы адресации** микрокоманд

Найдем разбиение  $\Pi_C$  и выполним оптимальную адресацию микрокоманд. Представим множество  $\Pi_C$  в виде  $\Pi_C^1 \cup \Pi_C^2$ . Пусть  $B_i \in \Pi_C^1$ , если класс  $B_i$  представляется одним интервалом R -мерного булева пространства. Если число интервалов, представляющих класс  $B_i \in \Pi_C$  больше единицы, то  $B_i \in \Pi_C^2$ . Очевидно,  $\Pi_C^1 \cap \Pi_C^2 = \emptyset$ , то есть, множество  $\Pi_C$  разбивается на два класса. Закодируем классы  $B_i \in \Pi_C^2$  двоичными кодами  $K(B_i)$  разрядности

$$R2 = \left| \log_2(\left| \Pi_C^2 \right| + 1) \right|. \tag{13}$$

Как и в КМУУ  $U_3$ , используем для кодирования классов  $B_i \in \Pi^2_C$  переменные  $\tau_r \in \tau$  . Однако теперь  $|\tau| = R_2$  и  $R_2 \le R_1$  .

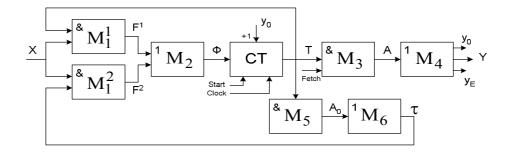

По исходной ГСА  $\Gamma$  может быть построена система обобщенных формул переходов [3] S. Разделим эту систему S на две подсистемы. Пусть подсистема  $S_1$  задает переходы для классов  $B_i \in \Pi^1_C$ , а подсистема  $S_2$  — для классов  $B_i \in \Pi^2_C$ . В этом случае для реализации схемы КМУУ на заказных матрицах предлагается модель  $U_4$  (рис. 3).

Рисунок 3 – Структурная схема КМУУ U<sub>4</sub>

В этой схеме матрица  $M_1$  разделена на две части. Матрица  $M_1^1$  реализует термы  $F^1$ , которые имеют вид (4). При этом значения некоторых переменных  $T_r \in T$  могут быть неопределёнными. Это связано с тем, что теперь часть  $A_m$  определяется кодов класса  $K(B_i)$ . Матрица  $M_1^2$  реализует систему функций  $F^2$ , которые являются термами вида (11). Матрица  $M_1^1$  соответствует подсистеме  $S_1$ , а матрица  $M_1^2$  — подсистеме  $S_2$ . Остальные матрицы  $(M_2,...,M_6)$  [6] имеют то же назначение, что и в КМУУ  $U_3$ . Разница между КМУУ  $U_3$  и  $U_4$  заключается в следующем:

- 1. Используются два источника кодов классов псевдоэквивалентных ОЛЦ. Один из них счетчик СТ, второй БПА.

- 2. Сложность реализации блока БПА в  $\rm U_4$  меньше, так как только часть классов  $\rm B_i \in \Pi_C$  необходимо кодировать.

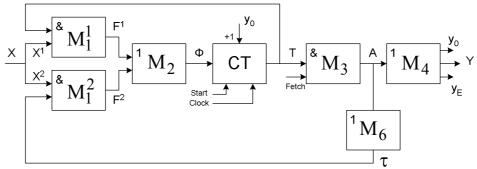

Отметим, что множество термов  $A_0$  представляет собой термы системы (10). Однако, некоторые из этих термов могут включать только часть переменных  $T_r \in T$ . Матрица  $M_5$  может быть удалена из схемы, если входом матрицы  $M_6$  будут выходы матрицы  $M_3$ . Это ведет к КМУУ  $U_5$  (рис. 4).

Рисунок 4 – Структурная схема КМУУ U<sub>5</sub>

Отметим, что матрица  $M_6$  также может быть удалена [6, 7]. При этом функции  $\tau_r \in \tau$  формируются непосредственно матрицей  $M_4$ . Это ведет к КМУУ  $U_6$ , схема которого может быть легко получена из схемы КМУУ  $U_5$ . Окончательный выбор между моделями  $U_2 - U_6$  делается на основе результатов синтеза их схем на заказных матрицах.

На рис. 3 — рис. 4 не показан триггер ТВ, что сделано для упрощения схемы. Отметим, что разбиение множества X на подмножества  $X^1$  и  $X^2$  также ведет к уменьшению сложности реализации по сравнению с КМУУ  $U_3$ .

#### Заключение

В работе предложено три структуры, позволяющие уменьшить сложность матричной реализации КМУУ с общей памятью. Предложенный метод основывается на использовании двух источников кодов классов псевдоэквивалентных ОЛЦ, что приводит к разбиению матрицы термов схемы адресации микрокоманд на две части.

Такой подход гарантирует уменьшение числа термов до величины, характерной для эквивалентного автомата Мили. При этом уменьшается площадь матриц блоков БАМ и БПА по сравнению с известными методами. Выбор структуры КМУУ может быть выполнен аналитическим путем (без синтеза всех вариантов реализации схемы). Направлением дальнейших исследований является разработка и исследование методов синтеза каждой из предложенных структур КМУУ.

Научная новизна статьи заключается в усовершенствовании метода синтеза КМУУ с общей памятью. Внесенные изменения позволяют использовать несколько источников кодов псевдоэквивалентных ОЛЦ, что, в свою очередь, предполагает использование одной из трех различных структур КМУУ для реализации исходного алгоритма управления.

Практическая значимость результатов работы заключается в уменьшении площади, занимаемой схемой КМУУ на кристалле. Это позволяет удешевить реализацию логических схем КМУУ, а также размещать более сложные цифровые системы на кристаллах меньшей площади

Дальнейшие исследования авторов будут направлены на исследование использования предложенных подходов в других современных элементных базисах, а также дальнейшее усовершенствование предложенных структур для уменьшения аппаратурных затрат при реализации в базисе заказных матриц.

## Литература

- 1. Smith M. Application-Specific Integrated Circuits. Boston: Addison-Wesley, 1997.

- 2. Baranov S. Logic Synthesis for Control Automata. Kluwer Academic Publishers, 1994. 312 pp.

- 3. Barkalov A., Titarenko L. Logic Synthesis for Compositional Microprogram Control Units. Berlin: Springer, 2008. 273pp.

- 4. Barkalov A.A., Titarenko L.A. Synthesis of operational and control automata // Donetsk: UNITECH, 2009. 256 pp.

- 5. Баркалов А.А. Синтез микропрограммных автоматов на заказных и программируемых СБИС / А.А.Баркалов, Л.А.Титаренко. Донецк.: ДонНТУ, Технопарк ДонНТУ УНИТЕХ, 2009. 336 с.

- 6. Barkalov A.A., Zelenyova I.J., Miroshkin A.N., Hathot Biayrek Approach to realization of comsitional microprogramming control unit with code converter on custom-made matrix // Наукові праці Донецького національного технічного університету. Серія: Інформатика, кібернетика та обчислювальна техніка. 2010. Вип. 11 (164). С. 71-74.

- 7. Баркалов А.А. Синтез устройства управления с разделением кодов и модификацией операторных линейных цепей / А.А.Баркалов, А.А.Красичков, А.Н.Мирошкин // Наукові праці Донецького національного технічного університету. Серія: Інформатика, кібернетика та обчислювальна техніка. 2008. Вип. 9(132). С. 183-187.

Надійшла до редакції 06.10.2010 Рецензент: канд. техн. наук, доц. Краснокутський В.О.

### О.О. Баркалов, І.Я. Зеленьова, С.О. Цололо, Х. Байрак

Донецький національний технічний університет

Розділення матриці термів при реалізації схеми композиційного мікропрограмного пристрою керування із загальною пам'яттю. У роботі запропоновані структури композиційного мікропрограмного пристрою керування із загальною пам'яттю, що дозволяють зменшити складність матричної реалізації схеми композиційного пристрою. Запропонований метод базується на використанні двох джерел кодів класів псевдоеквівалентних ОЛЛ, що призводить до розподілення матриці термів схеми адресації мікрокоманд на дві частини.

КМПК, ОЛЛ, загальна пам'ять, матрична реалізація, замовна матриця

#### A.A. Barkalov, I.Y.Zeleneva, S.A. Tsololo, H.Biayrek

Donetsk National Technical University

Separation of Term Matrix in the Scheme of Compositional Microprogram Control Unit with Shared Memory. The structures of compositional microprogram control unit with shared memory are proposed. Structures allow reducing the complexity of the matrix realization in the device's circuit. The proposed method is based on using two codes sources of classes pseudoequivalent OLC, which leads to the decomposition of the matrix terms in microinstruction addressing scheme into two parts.

CMCU, OLC, shared memory, matrix realization, gate array