УДК 681.3

С.Д. Погорелый Киевский национальный университет имени Тараса Шевченко sdp@univ.net.ua

## К вопросу формализации проектирования приложений для кластерных систем с GPU

Предложен метод повышения производительности кластерных систем, основанный на использовании видеоадаптеров компании NVIDIA с архитектурой FERMI в составе вычислительных узлов. Обоснована необходимость формализованного проектирования алгоритмов для таких систем, основанная на использовании математического аппарата модифицированных систем алгоритмических алгебр. Предложена организационная структура инструментальной системы алгоритмического проектирования с возможностью последующего синтеза программ, ассоцированных с параллельными алгоритмами. Описана предлагаемая методика проектирования и рассмотрен пример создания приложения. Приведены результаты ускорения при использовании предложенной методики и инструментальных средств.

SMP-архитектура, MPP-архитектура, CUDA-архитектура, инструментарий программирования для CUDA-архитектуры, модифицированные системы алгоритмических алгебр, организационная структура инструментальной системы проектирования параллельных алгоритмов, сеть Петри

#### Введение

Выводы экспертов области компьютерных технологий совпадают в том, что ресурс экстенсивного роста производительности компьютерных систем вследствие повышения сложности и тактовой частоты микропроцессоров себя исчерпал. В то же время существует большое разнообразие архитектур, которые могут обеспечить существенное повышение быстродействия алгоритмов, и важным классом среди них есть параллельные:

- SMP-архитектура (Рис. 1, отражает один уровень параллелизма);

- МРР-архитектура (Рис. 2, отражает два уровня параллелизма);

- CUDA-архитектура (при использовании в MPP-системах отражает три уровня параллелизма).

Эти аргументы делают актуальной задачу создания для них параллельных алгоритмов.

Рисунок 1 - SMP-архитектура

Рисунок 2 - МРР-архитектура

Последние исследования и разработки компании NVIDIA привели к созданию архитектуры FERMI [1], которая является наиболее продвинутой в истории вычислений на GPU и предлагает ряд новых возможностей:

- 512 ядер обеспечивают супервычисления и высокую производительность с минимальными затратами;

- позволяет широко использовать вычисления на GPU и CPU, поддерживая возможность работы с С ++ и совместимость со средой разработки Visual Studio, что упрощает параллельное программирование для этой архитектуры;

- имеет развитую иерархию системы памяти: регистровую, локальную, глобальную, коллективную, константную и текстурную.

Первая

версия

Mac OS X, Windows.

представлена

архитектур.

1. Инструментарий программирования CUDA SDK позволяет реализовывать на специальном упрощенном диалекте языка программирования ANSI C99 алгоритмы, которые будут выполняться на графических процессорах NVIDIA, и включать специальные функции в текст программы на С. Инструментарий дает разработчику возможность по своему усмотрению организовывать доступ к набору инструкций графического ускорителя, управлять его памятью, организовывать на нем сложные параллельные вычисления.

CUDA SDK

15.02.2007 г. Пакет использует grid-модель

памяти, кластерное моделирование потоков и

SIMD инструкции. Создан для платформ Linux,

для создания программных средств для этих

- 2. Инструментарий программирования OpenCL предназначен для написания компьютерных связанных С параллельными вычислениями на различных графических (GPU) и центральных (CPU) процессорах. Включает язык программирования, который базируется на **ANSI** стандарте C99, интерфейс программирования приложений API), (англ. библиотеки и динамическая система поддержки разработки программного обеспечения. OpenCL обеспечивает параллелизм на уровне инструкций и на уровне данных и является реализацией технологии GPGPU. OpenCL является полностью открытым стандартом.

- 3. Инструментарий программирования DirectX 11. В конце 2008 года на ежегодной конференции Gamefest компания Microsoft анонсировала новую версию популярного в мире графического АРІ -DirectX 11. Эта технология позволяет разработчикам использовать преимущества новейших разработок в области аппаратного обеспечения (это касается как СРU, так и GPU), а также упростить их работу. Официальная финальная версия вышла 22 октября 2009 года в составе Windows 7.

Динамика роста количества ядер в GPU существенно выше, чем в СРИ. В этой связи возникла новая технология - GPGPU. GPGPU (GPU общего назначения) техника использования графического процессора расчётов видеокарты ДЛЯ выполнения приложениях для общих вычислений, которые обычно проводит СРИ. Это обосновывает актуальность использования видеокарт с GPU и технологии GPGPU в системах MPP-архитектуры.

#### Проектирование параллельных алгоритмов

Инструментальные системы программирования, существующие в настоящее время, обеспечивают средства проектирования параллельных алгоритмов и синтеза соответствующих программ, в основном, одной парадигмы параллельного программирования. Это значительно затрудняет сравнение результатов применения различных подходов к разработке параллельных приложений. А, учитывая то, что таких подходов существует достаточно много, процесс анализа и выбора наилучшего становится практически невыполнимым.

Алгоритмический этап проектирования параллельных приложений является начальным и наименее технологически обеспеченным. Однако, он влияет на весь дальнейший процесс разработки и определяет ее успех в целом. Инструментарий этого этапа проектирования должен обеспечивать:

- эффективные средства описания алгоритмов функционирования систем параллельной обработки данных с учетом их специфики;

- возможность формальных эквивалентных преобразований алгоритмов с целью получения новых более продуктивных версий;

- средства описания последовательных и параллельных фрагментов алгоритмов, возможность генерации ассоциированных с исследуемыми алгоритмами программ для различных подходов параллельного программирования;

- удобные визуальные средства проектирования алгоритмов;

- возможность оценки темпоральных характеристик работы алгоритмов перед их использованием на целевых параллельных аппаратно-программных платформах.

Перечисленные требования выдвигают задачу формализованного проектирования параллельных алгоритмов, для чего предлагается использовать математический аппарат модифицированных систем алгоритмических алгебр [2 – 6]. Этот выбор целесообразен в силу следующих причин:

- математический аппарат САА-М ориентирован на проектирование параллельных алгоритмов и ассоциированных с ними программ;

- любой алгоритм, записанный в САА-М, представляет собой алгебраическую формулу, позволяющую применять систему развитых в САА-М формальных эквивалентных преобразований для оптимизации и дальнейшего автоматизированного синтеза программного обеспечения;

- САА-М соответствуют концепции структурного программирования;

• методология проектирования должна базироваться не только и не столько на коммерческих продуктах, сколько на научном фундаменте.

формирования Опишем методику параллельной схемы для SMP-архитектуры на примере алгоритма Данцига (широко применяется решения задачи маршрутизации компьютерных сетях, основывается на матричных вычислениях и имеет полиномиальную сложность  $O(n^3)$ . Идея заключается в последовательном рекуррентной помощью формировании c процедуры подматриц кратчайших растущей размерности. Каждая такая матрица фактически является матрицей кратчайших путей подграфов с вершинами от 0 до m-1.

1. Вначале следует сформировать последовательную схему алгоритма. С учетом приведенных в статье обозначений ее можно записать в виде соотношения:

$Dancig = \{ SubDanc1(m) \times SubDanc2(m) \times SubDanc3(m) \times (++m) \}$

- 2. Необходимо определить концепции распараллеливания, причем, в связи стем, что выполняется распараллеливание алгоритма по данным, размещенным в памяти (каждый поток обрабатывает определенную часть информационной множества), следует решить вопрос их разбиения.

- 3. Необходимо сформировать параллельную схему алгоритма, основываясь на необходимости обеспечения максимального параллелизма в работе потоков.

- 4. Основываясь на системе эквивалентных преобразований в САА-М и формируя различные критерии трансформаций, получить совокупность параллельных схем, обеспечивающих различные параметры соответствующих вычислительных процедур.

- 5. Исследовать полученные схемы (анализ, моделирование и т.д.) с целью выбора максимально соответствующей нужным требованиям.

Выполняя указанные действия, получим следующие две схемы алгоритма (методика с указанием всех обозначений описана в [7]):

$$Dancig = \left\{ \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub1(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub2(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2N} \left( PSub3(m,2N,l) \times B_{2N}(l) \right) \right) \times \left( \dot{\bigvee}_{l=1}^{2$$

$Dancig = \{ \bigvee_{m>N}^{2N} \left( PSub1(m,2N,l) \times B_{2N}(l) \times PSub2(m,2N,l) \times B_{2N}(l) \times PSub3(m,2N,l) \times B_{2N}(l) \right) \times PSub3(m,2N,l) \times PSub3(m,2N$

$$\times (++m) \} = \bigvee_{l=1}^{2N} \{ PSub1(m,2N,l) \times B_{2N}(l) \times PSub2(m,2N,l) \times B_{2N}(l) \times PSub3(m,2N,l) \times B_{2N}(l) \times (++m) \}$$

$$(2)$$

Выполнив эквивалентные преобразования схемы (1) в САА-М, получим схему (3):

$$Dancig = \bigvee_{l=1}^{2N} \left\{ \left( \left( PSub1(m, N, l) \vee PSub2(m, N, l) \right) \times B_{2N}(l) \right) \times \left( \left( PSub3(m, 2N, l) \times B_{2N}(l) \right) \right) \times (++m) \right\}$$

$$(3)$$

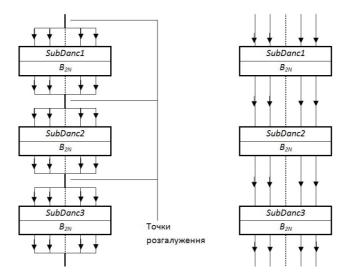

Схемы (1) и (2), фактически, отражают две модели синхронизации потоков (рис. 3). Преимуществом схемы (3) является меньшее количество синхронизаций, что повышает эффективность её работы.

Благодаря параллельности выполнения первых двух операций можно существенно

уменьшить общее количество операций синхронизации, а поскольку это операции, которые нельзя распараллелить, получим выигрыш во времени за счет некоторого увеличения нагрузки на отдельные потоки.

Рисунок 3 - Модели синхронизации потоков

# Организационная структура инструментальной системы проектирования параллельных алгоритмов

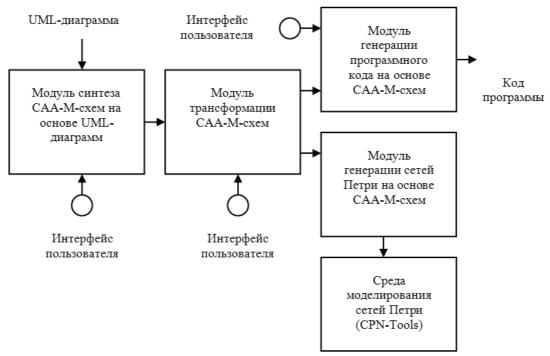

На рис. 4 представлена организационная структура инструментального комплекса для проектирования параллельных алгоритмов и ассоциированных с ними программ.

Модуль синтеза CAA-M-схем на основе UML-диаграмм позволяет осуществить два уровня параметризации входных данных:

- на уровне САА-М-схем алгоритмов;

- на уровне UML-диаграмм.

Модуль трансформации САА-М-схем развитой алгоритмов на основе алгоритмических алгебрах системы эквивалентных трансформаций позволяет совокупность схем получить параллельного различным поведением алгоритма c характеристиками.

Рисунок 4 - Организационная структура инструментального комплекса

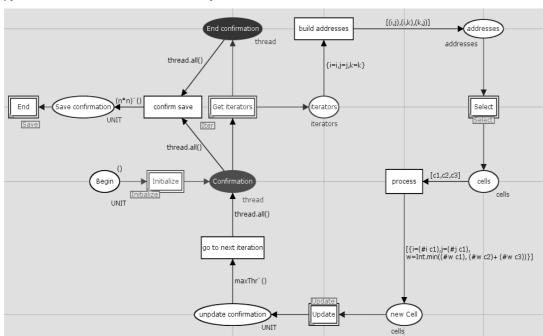

Для любой из полученных САА-М-схем соответствующий модуль алгоритмов возможность сгенерировать цветную сеть Петри, моделирование которой позволяет получить темпоральные оценки параллельных алгоритмов. На рис. 5 представлена цветная сеть Петри для параллельного алгоритма Данцига, соответствующая схеме (3). В конечном счете, для выбранной схемы (схем) осуществляется синтез параллельной программы (программ) определенной парадигмы параллельного программ ирования.

архитектурой FERMI рассмотрим на примере алгоритма Флойда-Уоршала, который решает задачу определения кратчайших путей на взвешенном графе, основывается на матричных вычислениях и имеет полиномиальную сложность  $O(n^3)$ . На видеоадаптерах целесообразно реализовать ту его часть, которая касается регулярных матричных вычислений: обработку матриц весов кратчайших путей D и предшествования P [8]. После применения предложенного подхода получим фрагменты схем алгоритма, которые выполняются на GPU:

#### Параллельная схема алгоритма Флойда-Уоршала для MPP-архитектуры с GPU

Методику создания приложения для MPPархитектур с использованием видеоадаптеров с

Рисунок 5 - Цветная сеть Петри для алгоритма Данцига

$$GPUBlock1 := S(\beta) * \left[ {{nThread} \atop {\stackrel{\circ}{\bigvee}} {\left( {Cell\, \operatorname{Re}\, aliz} \right)}} \right] * T(\alpha)) \tag{4}$$

$$GPUBlock2 := S(\beta) * \left[ {nThread \atop \overset{\bullet}{\bigvee}}_{s'=1} \left( Column \operatorname{Re} aliz \right) \right] * T(\alpha))$$

(5)

Подставляя (4) и (5) в схему алгоритма Флойда-Уоршала, получаем общую схему, реализующую МРІ-парадигму кластерных вычислений с использованием видеоадаптеров [X]. По полученной схеме алгоритма было синтезировано приложение, которое выполнялось на кластере, содержащем 4 узла с видеоадаптерами GEForce430GT (архитектура

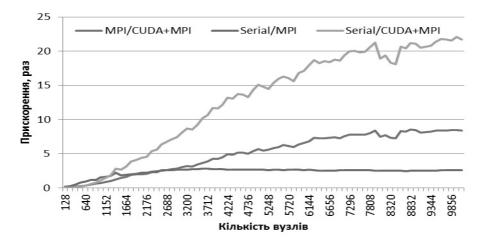

FERMI). Общее ускорение быстродействия для различных реализаций алгоритма Флойда-Уоршала:

- последовательная реализация на одном компьютере,

- (МРІ-парадигма с видеоадаптерами, 4 узла)/(МРІ-парадигма, 4 узла),

• (МРІ-парадигма с видеоадаптерами, 4 узла)/(последовательная реализация на одном компьютере)

представлено на рис. 6 (по вертикальной оси отложено ускорение (в разах), по горизонтальной – количество n вершин графа). Приведенные

зависимости позволяют сделать оценку, что при использовании старших моделей видеоадаптеров ряда с архитектурой FERMI компании NVIDIA, может быть достигнуто ускорение быстродействия в 80 – 100 раз.

Рисунок 6 - Ускорение вычислений для различных реализаций алгоритма

#### Выводы

- 1. Разработаны концепция и организационная структура системы проектирования параллельных алгоритмов (технология GPGPU), включающая следующие возможности:

- нотации исходных (проектируемых) алгоритмов в виде:

- САА-М-схем,

- UML-диаграмм;

- эквивалентных преобразований схем алгоритмов в САА-М;

- моделирования схем параллельных алгоритмов, представленных в виде сетей Петри в среде CPN Tools;

- генерации параллельных приложений для различных парадигм параллельного программирования и используемых инструментальных средств.

- Математический аппарат CAA-M B. Глушкова является гибким, удобным эффективным средством аналитического исследования и анализа параллельных схем алгоритмов, что позволяет сосредоточиться на методологии проектирования системы, концепциях методах трансформации параллельных схем, абстрагируясь от конкретных деталей реализации. В результате полученные базой схемы являются для создания соответствующего программного обеспечения.

#### Список литературы

- 1. Анализ методов повышения производительности компьютеров с использованием графических процессоров и программно-аппаратной платформы CUDA / С.Д. Погорелый, Ю.В. Бойко, М.И. Трибрат, Д.Б. Грязнов // Математичні машини і системи. 2010. №1. С. 40 54.

- 2. Pogorilyy S.D. Finding Strongly Connected Components In Parallel / S.D. Pogorilyy, S.I. Lozytskyi // Applied and Computational Mathematics. -2007.-V 6 No 2.-P.121-130.

- 3. Formalized Methods of paralleling the Goldberg-Tarjan Algorithm / S.D. Pogorillyy, Yu.V. Boyko, S.I. Lozitskiy, A.D. Gusarov // Journal of Automation and Information Sciences. 2008. V 40. No 9. P. 64-75.

- 4. Pogorilyy S.D. Paralleling Of Edmonds-Karp Net Flow Algorithm / Pogorilyy S.D. Y, Gusarov A.D. // Appl. Comput. Math. -2006. -V. 5. -N0.2. -P1.21-130.

- 5. An approach to the parallel solution of a high-dimensional basic flow problem / S. D. Pogorilyy, Yu. V. Boyko, A. D. Gusarov, S. I. Lozytskyi // Cybernetics and Systems Analysis, Volume 45, Issue 2 (March 2009) pages: 291 296. Springer Science and Business Media Inc. ISSN:1060-0396.

- 6. Pogorilyy S.D. A Conception for Creating a System of Parametric Design of Parallel Algorithms and their Software Implementations / S.D. Pogorilyy and I. Yu. Shkulipa // Cybernetics and System Analysis, Volume 45, Issue 6 (November 2009) pages: 952 958. Springer Science and Business Media Inc. ISSN:1060-0396.

- 7. Дослідження паралельних схем алгоритму Данцига для обчислювальних систем зі спільною пам'яттю / С.Д. Погорілий, В.А. Мар'яновський, Ю.В. Бойко, О.А. Верещинський // Математичні машини і системи. 2009. №4. С. 27-37.

- 8. С.Д. Погорілий Вітель. Формування узагальнених паралельних схем алгоритму Флойда-Уоршала / С.Д. Погорілий, В.А. Мар'яновський, Ю.В. Бойко // Системні дослідження та інформаційні технології. – 2010. – №1. – С. 52 – 68.

Надійшла до редколегії 10.10.2011

#### С.Д. ПОГОРІЛИЙ

Київський національний університет імені Тараса Шевченка

### До питання формалізації проектування додатків для кластерних систем з GPU

Запропоновано метод підвищення продуктивності кластерних систем, заснований на використанні відеоадаптерів компанії NVIDIA з архітектурою обчислювальних **FERMI** складі В вузлів. Обгрунтовано необхідність формалізованого проектування алгоритмів для таких систем. Запропонована організаційна структура інструментальної системи алгоритмічного проектування з можливістю подальшого синтезу програм, асоційованих 3 паралельними алгоритмами. Описана пропонована методика проектування і розглянуто приклад створення програми. Наведено результати прискорення при використанні запропонованої методики інструментальних засобів.

SMP-архітектура, MPP-архітектура, CUDAархітектура, інструментарій програмування для CUDA-архітектури, модифіковані системи алгоритмічних алгебр, організаційна структура інструментальної системи проектування паралельних алгоритмів, мережа Петрі

#### S. D. POGORILY

Kyiv National Taras Shevchenko University

## On the Problem of Formalization of Designing Applications for Cluster Systems with GPU

A method of improving performance of cluster systems based on the use of video cards from NVIDIA's FERMI architecture consisting of computing nodes is proposed. Necessity of formal design algorithms for such systems is shown. Organizational structure of algorithmic design tool with the possibility of further synthesis of programs associated with parallel algorithms is proposed. The proposed design procedure is described and an example of the program is considered. The results of acceleration when using the proposed methodology and tools are provided.

SMP-architecture, MPP-architecture, CUDAarchitecture, programming tools for CUDAarchitecture, modified systems of algorithmic algebras, the structure of the instrumental design of parallel algorithms, Petri nets