# СИНТЕЗ КОМПОЗИЦИОННОГО МИКРОПРОГРАММНОГО УСТРОЙСТВА УПРАВЛЕНИЯ НА FPGA

# Баркалов А.А., Ковалев С.А., Ефименко К.Н.

Донецкий национальный технический университет, г. Донецк кафедра электронных вычислительных машин E-mail: barkalov@cs.dgtu.donetsk.ua

### Abstract

Barkalov A.A., Kovalev S.A., Efimenko K.N. Synthesis of compositional microprogram control unit of FPGA. The method of compositional microprogram control unit (CMCU) design permitting to decrease the amount of functions of addressing FSM depending on logic conditions and internal variables ifs proposed. Method is oriented on the application in the basis of FPGA. The method is based on the usage of the senior bits of the operational linear chains output address to initialize the transitions between different operational linear chains. The application of proposed method permits to decrease the amount of LUT-elements of FPGA, needed for implementation of CMCU.

### 1. Введение

Устройство управления (УУ) является одной из основных частей любой цифровой системы [1]. Успехи микроэлектроники привели к появлению «систем—на—кристалле», произвольная логика в которых, как правило, реализуется на FPGA (field—programmable gate array) [2,3]. В этой связи возникает необходимость разработки новых и совершенствования известных методов синтеза УУ, ориентированных на этот базис.

Характерной особенностью FPGA является наличие логических элементов табличного типа, так называемых LUT-элементов (look-up table). Число входов LUTэлементов ограничено и не превышает 6 [2,3], что вызывает необходимость функциональной декомпозиции систем булевых функций, задающих закон функционирования УУ [4]. Один из путей уменьшения числа LUT-элементов в схеме УУ — уменьшение числа функций с большим числом аргументов. В литературе решению этой задачи уделялось достаточно большое внимание [5,6]. Однако и в настоящее время она остается актуальной. Наиболее эффективным путем решения рассматриваемой задачи может быть переход к двухуровневой структуре УУ, в которой система выходных функций (микроопераций) определена более, чем на 50% возможных термов. В этом случае для реализации системы микроопераций целесообразно использовать блоки ЕАВ (етbedded array block), входящие в состав современных систем на кристалле [2,3]. При таком подходе управляющая память, реализованная на основе ЕАВ, хранит микрокоманды, а произвольная логика их адресации реализуется на FPGA. Ограниченность ресурсов ЕАВ вызывает необходимость уменьшения разрядности микрокоманд. Всем этим целям идеально отвечают композиционные микропрограммные устройства управления (КМУУ), управляющая память которых не содержит адресов переходов [7]. В настоящей работе предлагается метод синтеза КМУУ с минимально возможным числом выходов схемы адресации микрокоманд.

## 2. Основные определения

Пусть алгоритм управления цифровой системы задан в виде граф—схемы алгоритма (ГСА)  $\Gamma$  [8], операторные вершины которой образуют множество  $B = \{b_1, ..., b_K\}$ . В вершине  $b_k \in B$  записан набор одновременно выполняемых микроопераций (микрокоманда)  $Y(b_k) \subseteq Y$ , где  $Y = \{y_1, ..., y_N\}$ . В условных вершинах ГСА  $\Gamma$  записываются элементы множества логических условий  $X = \{x_1, ..., x_L\}$ . Кроме операторных и условных вершин ГСА  $\Gamma$  содержит начальную  $b_0$  и конечную вершины  $b_E$ . Пусть E — множество дуг  $\Gamma$ СА  $\Gamma$ .

Наукові праці ДонНТУ Випуск 106

Введём ряд определений [7], необходимых для дальнейшего изложения материала.

Определение 1. Операторной линейной цепью (ОЛЦ) ГСА  $\Gamma$  называется конечная последовательность операторных вершин  $\alpha_g = (b_{g1},...,\ b_{gF_g})$ , такая что для любой пары соседних компонент кортежа  $\alpha_g$  существует дуга <  $b_{gi}$ ,  $b_{gi+1}>$   $\in$  E, где i — номер компоненты кортежа  $\alpha_g$  ( $i=1,\ldots,F_g-1$ ).

Определение 2. Входом ОЛЦ  $\alpha_g$  называется вершина  $b_q$  ∈ B, такая что существует дуга <b<sub>t</sub>,  $b_q$ > ∈ E, где  $b_t$  — условная или начальная вершина ГСА  $\Gamma$ , или операторная вершина, не входящая в ОЛЦ  $\alpha_g$ .

Определение 3. Выходом ОЛЦ  $\alpha_g$  называется вершина  $b_q \in B$ , такая что существует дуга  $<\!b_q$ ,  $b_t\!> \in E$ , где  $b_t$  — условная или конечная вершина ГСА  $\Gamma$ , или операторная вершина, не входящая в ОЛЦ  $\alpha_g$ .

Обозначим через  $D^g \subseteq B$  множество операторных вершин, входящих в ОЛЦ  $\alpha_g \in C$ , где  $C = \{\alpha_1, ..., \alpha_G\}$  — множество ОЛЦ ГСА  $\Gamma$ , удовлетворяющее условию

$$D^{g} \cap D^{q} = 0 \ (g \neq q, g, q \in \{1, ..., G\});$$

$$B = D^{1} \cup D^{2} \cup ... \cup D^{G};$$

$$D^{g} \neq 0 \ (g = 1, ..., G).$$

(1)

Пусть для каждой ОЛЦ  $\alpha_g \in C$  выполнена естественная адресация микрокоманд

$$A(b_{gi+1}) = A(b_{gi}) + 1$$

$(i = \overline{1, F_g - 1}),$  (2)

где  $A(b_q)$  — адрес микрокоманды, соответствующей вершине  $b_q \in B$ .

В этом случае ГСА  $\Gamma$  может быть интерпретирована КМУУ с базовой структурой (рис. 1), называемым в дальнейшем КМУУ  $U_1$ .

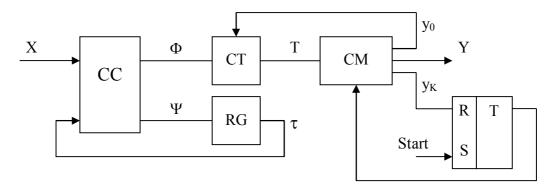

Рисунок 1 — Структурная схема КМУУ U<sub>1</sub>

Здесь комбинационная схема СС и регистр RG образуют автомат адресации микрокоманд  $S_1$ , а счетчик СТ, управляющая память СМ и триггер Т образуют микропрограммное устройство управления  $S_2$  с естественной адресацией микрокоманд [9], что соответствует условию (2). Регистр RG хранит код  $K(a_m)$  текущего состояния  $a_m \in A$ , где  $A = \{a_1, ..., a_M\}$  — множество внутренних состояний автомата адресации, и имеет R разрядов, где  $R = ]log_2M[$ . Для кодирования состояний  $a_m \in A$  используются переменные  $\tau_r \in \tau = \{\tau_1, ..., \tau_R\}$ , регистр RG имеет входы типа D. Счетчик СТ хранит адреса  $A(b_k)$  микрокоманд, представляемых переменными  $T_r \in T = \{T_1, ..., T_{R_1}\}$ , где  $R_1 = ]log_2K[$ . Микрокоманды  $Y(b_k)$  хранятся в управляющей памяти, имеющей в случае унитарного кодирования микроопераций [9]  $2^{R_1} \times (N+2)$ бит. Один из дополнительных разрядов используется для хранения сигнала  $y_0$ , по которому осуществляется режим адресации (2), второй — для хранения сигнала  $y_K$ , по которому происходит завершение функционирования устройства.

По сигналу Start содержимое RG и CT обнуляются, что соответствует исходному состоянию КМУУ, триггер T устанавливается в единицу, что позволяет считывать микрокоманды из CM. При переходах внугри ОЛЦ  $\alpha_g \in C$  сигнал  $y_0 = 1$ , при этом состояние автомата  $S_1$  не меняется. Если выход текущей ОЛЦ достигнут, то  $y_0 = 0$  и автомат  $S_1$  формирует функции возбуждения регистра  $\Psi = \{\Psi_1, ..., \Psi_R\}$  и счетчика  $\Phi = \{\Phi_1, ..., \Phi_{R1}\}$

$$\Phi = \Phi (\tau, X),

\Psi = \Psi (\tau, X).$$

(3)

Функции Ф и  $\Psi$  формируют в регистре код  $K(a_S)$  состояния перехода автомата  $S_1$  и адрес входа очередной ОЛЦ  $\alpha_g \in C$  в счетчике соответственно. При достижении микрокоманды  $Y(b_k) \subseteq Y$  такой, что  $\langle b_k, b_E \rangle \in E$ , формируется сигнал  $y_K = 1$ , триггер T обнуляется и функционирование КМУУ  $U_1$  прекращается.

Такие УУ имеют ряд положительных качеств [7], делающих целесообразным их применение в системах на кристалле:

- 1. Число функций с числом аргументов до L+R ограничено параметром  $t_1=R+R_1$ , что позволяет уменьшить число LUT–элементов в схеме УУ по сравнению, например, с реализацией УУ в виде микропрограммного автомата [8].

- 2. Управляющая память содержит только микрооперации  $y_n \in Y$  и не содержит адреса переходов, что при принятой стратегии кодирования микроопераций [9] минимизирует требуемое число выходов блоков EAB.

- 3. Согласно условию (1), число микрокоманд в СМ равняется K, что является минимально возможным параметром для микропрограммных устройств управления [9]. Это позволяет минимизировать ёмкость используемых блоков EAB.

Итак, использование модели КМУУ для интерпретации ГСА позволяет уменьшить число LUT-элементов в схеме УУ и использовать минимально возможные ресурсы блоков EAB для реализации системы микроопераций. В настоящей работе предлагается метод уменьшения числа выходов схемы СС, что приводит к дальнейшему уменьшению числа LUT-элементов в схеме УУ.

### 3. Основная идея метода

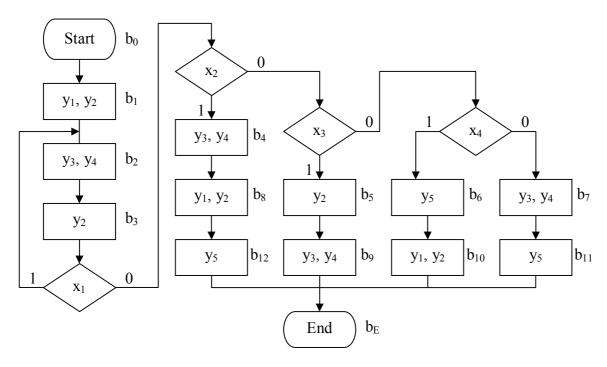

Пусть алгоритм управления цифровой системы задан ГСА  $\Gamma_1$  (рис. 2).

Используем результаты работы [7] и построим для ГСА  $\Gamma_1$  множество  $C=\{\alpha_1,\,\alpha_2,\,\dots\,\alpha_5\}$ , где  $\alpha_1=< b_1,\,b_2,\,b_3>,\,\alpha_2=< b_4,\,b_8,\,b_{12}>,\,\alpha_3=< b_5,\,b_9>,\,\alpha_4=< b_6,\,b_{10}>,\,\alpha_5=< b_7,\,b_{11}>$ . Очевидно, что полученное множество C удовлетворяет условию (1). Выполним адресацию микрокоманд (2) и построим таблицу содержимого управляющей памяти (табл. 1).

| Таблица 1 — | Солержимое | управляющей памяти | KM    | VV I | $\Box_1$ ( | $(\Gamma_1)$ | ١ |

|-------------|------------|--------------------|-------|------|------------|--------------|---|

| таолица т — | СОДСОЖИМОС | индавлиющей намини | 1/1/1 | ,,,, | J 1        |              | , |

| $A(b_k)$ | $Y(b_k)$                                     | Комментарии                   | $A(b_k)$ | $Y(b_k)$                                     | Комментарии                   |

|----------|----------------------------------------------|-------------------------------|----------|----------------------------------------------|-------------------------------|

| 0000     | y <sub>0</sub> y <sub>1</sub> y <sub>2</sub> | $b_1 I_1^{-1}$                | 0110     | y <sub>0</sub> y <sub>2</sub>                | $b_5 I_3^1$                   |

| 0001     | y <sub>0</sub> y <sub>3</sub> y <sub>4</sub> | $b_2 I_1^2$                   | 0111     | y3 y4 y <sub>K</sub>                         | b <sub>9</sub> O <sub>3</sub> |

| 0010     | <b>y</b> <sub>2</sub>                        | b <sub>3</sub> O <sub>1</sub> | 1000     | y <sub>0</sub> y <sub>5</sub>                | $b_6 I_4^{1}$                 |

| 0011     | y <sub>0</sub> y <sub>3</sub> y <sub>4</sub> | $b_4 I_2^{-1}$                | 1001     | y <sub>1</sub> y <sub>2</sub> y <sub>K</sub> | $b_{10} O_4$                  |

| 0100     | y <sub>0</sub> y <sub>1</sub> y <sub>2</sub> | b <sub>8</sub>                | 1010     | y <sub>0</sub> y <sub>3</sub> y <sub>4</sub> | $b_7 I_5^1$                   |

| 0101     | <b>У</b> 5 <b>У</b> К                        | $b_{12} O_2$                  | 1011     | y5 y <sub>K</sub>                            | $b_{11} O_5$                  |

Здесь  $U_1$  ( $\Gamma_1$ ) обозначает, что КМУУ  $U_1$  интерпретирует ГСА  $\Gamma_1$ ,  $I_g^{\ j}$  — j-й вход g-й ОЛЦ ( $j \le F_g$ ),  $O_g$  — выход g-й ОЛЦ ( $g = \overline{1, G}$ ).

Как видно из табл. 1, все вершины, кроме выходов ОЛЦ, содержат сигнал  $y_0$  для организации режима адресации (2), вершины, связанные с конечной вершиной  $b_E$ , содержат сигнал  $y_K$  для организации режима останова.

Наукові праці ДонНТУ Випуск 106

Рисунок 2 — Исходная граф-схема алгоритма  $\Gamma_1$

Как видно из табл. 1, старшие  $R_2=3$  разряда адресов выходов ОЛЦ  $\alpha_g$   $\in$  С для всех ОЛЦ имеют разные значения. В общем случае

$$R_2 = \log_2 G [. (4)$$

Таким образом, старшие  $R_2$  разряда адреса выхода ОЛЦ могут использоваться для её однозначной идентификации.

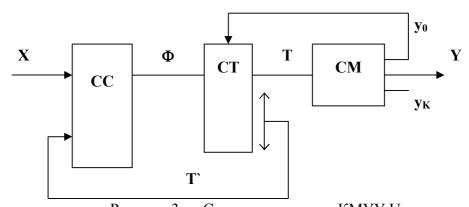

В настоящей работе предлагается использовать это свойство для минимизации числа выходов схемы CC, чему соответствует композиционное микропрограммное устройство управления  $U_2$  (рис. 3). Организация режима останова в КМУУ  $U_1$  и  $U_2$  идентична, поэтому триггер T на рис. 3 не показан.

Рисунок 3 — Структурная схема КМУУ U<sub>2</sub>

Принцип функционирования КМУУ  $U_1$  и  $U_2$  отличается только при организации перехода между различными ОЛЦ  $\alpha_g \in C$ . В этом случае сигнал  $y_0$  не формируется и адрес входа очередной ОЛЦ заносится в СТ функциями

$$\Phi = \Phi (T', X), \tag{5}$$

Наукові праці ДонНТУ Випуск 106

где  $T`\subseteq T$ ,  $|T`|=R_2$ ,  $T`=\{T_1,\ ...,\ T_{R_2}\}$ . В настоящей работе предлагается метод синтеза КМУУ  $U_2$ .

- **4. Метод синтеза композиционного микропрограммного устройства управления U\_2** Предлагаемый в работе метод синтеза КМУУ  $U_2$  включает следующие этапы:

- 1. Формирование множества ОЛЦ, адресация микрокоманд и формирование содержимого управляющей памяти. Этот этап выполняется по известной методике [7]. Для КМУУ  $U_2(\Gamma_1)$   $R_2 = 3$ ,  $T` = \{T_1, T_2, T_3\}$ .

- 2. <u>Формирование таблицы переходов КМУУ.</u> Эта таблица является основой для формирования системы функций (5) и последующего синтеза схемы СС.

Таблица переходов КМУУ  $U_2$  содержит столбцы:  $O_g$ ,  $SA(O_g)$ ,  $I_q^j$ ,  $A(I_q^j)$ ,  $X_h$ ,  $\Phi_h$ , h, где  $O_g$  — выход ОЛЦ  $\alpha_g \in C$ ;  $SA(O_g)$  — старшие  $R_2$  разрядов адреса микрокоманды, соответствующей выходу ОЛЦ  $\alpha_g \in C$ ;  $I_q^j$  — j-й вход ОЛЦ  $\alpha_g \in C$  ( $j = \overline{1, F_g - 1}$ );  $A(I_q^j)$  — адрес входа  $I_q^j$ ;  $X_h$  — входной сигнал, определяющий переключение счетчика CT из адреса выхода ОЛЦ  $\alpha_g$   $A(O_g)$  в адрес входа  $A(I_q^j)$ ;  $\Phi_h \subseteq \Phi$  — набор функций возбуждения счетчика CT, принимающих единичное значение для переключения CT из  $A(O_g)$  в  $A(I_q^j)$ ;  $h = \overline{1,H}$  — номер перехода.

Для КМУУ  $U_2$  ( $\Gamma_1$ ) таблица переходов (табл. 2) содержит H = 5 строк.

|         | Таол      | ица 2 — таол | пица переходо | JB KIVI Y Y U2 (                                | (I <sub>1</sub> )                            |   |

|---------|-----------|--------------|---------------|-------------------------------------------------|----------------------------------------------|---|

| $O_{g}$ | $SA(O_g)$ | $I_q^{\ j}$  | $A(I_q^{j})$  | $X_h$                                           | $\Phi_{h}$                                   | h |

| $O_1$   | 001       | $I_1^2$      | 0001          | $\mathbf{x}_1$                                  | $D_4$                                        | 1 |

|         |           | $I_2^{1}$    | 0011          | $\frac{-}{x_1}x_2$                              | $D_3D_4$                                     | 2 |

|         |           | $I_3^1$      | 0110          | $\overline{x_1}\overline{x_2}x_3$               | $D_2D_3$                                     | 3 |

|         |           | $I_2^1$      | 1000          | $\overline{x_1}\overline{x_2}\overline{x_3}x_4$ | $D_1$                                        | 4 |

|         |           | $I_3^1$      | 1011          | $\overline{x_1x_2}\overline{x_3x_4}$            | D <sub>1</sub> D <sub>3</sub> D <sub>4</sub> | 5 |

Таблица 2 — Таблица переходов КМУУ U<sub>2</sub> (Г<sub>1</sub>)

Отметим, что переходы из выходов ОЛЦ  $\alpha_g \in C$ , связанных с конечной вершиной, не рассматриваются. Это связано с тем, что при достижении таких выходов функционирование КМУУ  $U_2$  прекращается.

3. <u>Формирование системы функций возбуждения счетчика.</u> Система (5) формируется по таблице переходов КМУУ  $U_2$  в виде

$$\varphi_{\mathbf{r}} = \bigvee_{h=1}^{\mathbf{H}} \mathbf{C}_{\mathbf{r}h} \, \mathbf{E}_{\mathbf{g}}^{\mathbf{h}} \, \mathbf{X}_{\mathbf{h}} \, \left( \mathbf{r} = \overline{1, \mathbf{R}_{\mathbf{1}}} \right) \tag{6}$$

Здесь  $C_{rh}$  — булева переменная, равная единице, если и только если в h-й строке таблицы переходов записана функция  $\varphi_r = 1$  (h =  $\overline{1,H}$ );  $E_g^h$  — конъюнкция переменных  $T_r \in T$ , соответствующая адресу  $SA(O_g)$  выхода  $O_g$  из h-й строки таблицы:

$$E_g^h = \bigwedge_{r=1}^{R_2} T_r^{lgr}, \qquad (7)$$

где lgr  $\in \{0, 1\}$  — значение r-го разряда адреса  $SA(O_g)$ ,

$$T_r^{\circ} = \overline{T_r}, \quad T_r^1 = T_r \quad (r = \overline{1, R_2}).$$

Использование выражений (6) и (7) для нашего примера приводит к системе (5) в виде:

$$\begin{split} &D_1 = \overline{T_1} \, \overline{T_2} \, T_3 \, \overline{x_1} \, \overline{x_2} \, \overline{x_3} \, x_4 \vee \overline{T_1} \, \overline{T_2} \, T_3 \, \overline{x_1} \, \overline{x_2} \, \overline{x_3} \, x_4 \,, \\ &D_2 = \overline{T_1} \, \overline{T_2} \, T_3 \, \overline{x_1} \, \overline{x_2} \, x_3 \,, \\ &D_3 = \overline{T_1} \, \overline{T_2} \, \overline{T_3} \, \overline{x_1} \, \overline{x_2} \vee \overline{T_1} \, \overline{T_2} \, \overline{T_3} \, \overline{x_1} \, \overline{x_2} \, x_3 \vee \overline{T_1} \, \overline{T_2} \, \overline{T_3} \, \overline{x_1} \, \overline{x_2} \, x_3 \, x_4 \,, \\ &D_4 = \overline{T_1} \, \overline{T_2} \, T_3 \, \overline{x_1} \vee \overline{T_1} \, \overline{T_2} \, \overline{T_3} \, \overline{x_1} \, \overline{x_2} \vee \overline{T_1} \, \overline{T_2} \, \overline{T_3} \, \overline{x_1} \, \overline{x_2} \, \overline{x_3} \, \overline{x_4} \,, \end{split}$$

4. Синтез логической схемы КМУУ. Синтез сводится к реализации системы (5) на FPGA и реализации управляющей памяти на EAB. Вторая из этих задач является тривиальной, а первая достаточно полно рассмотрена в литературе [4]. Вопросы синтеза схемы КМУУ  $U_2$  выходят за рамки нашей статьи.

Моделирование предлагаемого метода показало, что уменьшение числа LUT— элементов по сравнению с базовой структурой определяется соотношением между величинами R и  $R_1$ , и может быть выражено коэффициентом

$$\eta = \frac{R + R_1}{R_1} = 1 + \frac{R}{R_1} \tag{8}$$

### 5. Заключение

Предлагаемый в работе метод синтеза КМУУ позволяет сократить число функций, реализуемых на LUT-элементах, от  $t_1$  = R +  $R_1$  (КМУУ с базовой структурой) до  $t_2$  =  $R_1$ . Как показали исследования авторов, оптимизация числа LUT-элементов в схеме КМУУ  $U_2$  по сравнению с КМУУ  $U_1$  пропорциональна коэффициенту  $\eta$  (8).

При этом время такта КМУУ  $U_1$  и  $U_2$  совпадает, то есть оптимизация по аппаратурным затратам не приводит к потере производительности. Недостаток метода заключается в увеличении числа сигналов обратной связи в КМУУ  $U_2$  при выполнении условия

$$R_2 > R. \tag{9}$$

Как показали исследования, предлагаемый метод целесообразно применять, если условие (9) нарушается, то есть при  $R_2=R$ . В этом случае число LUT—элементов в схеме СС КМУУ  $U_2$  может уменьшаться на 35–42% по сравнению с аналогичным параметром КМУУ  $U_1$ .

### Литература

- 1. Баркалов А. А. Синтез операционных устройств. Донецк: ДонНТУ, 2003. 306 с.

- 2. Salcic Z. VHDL and FPLD<sub>S</sub> in digital systems design, prototyping and customization. Kluwer Academic Publishess, 1998. 549 p.

- 3. Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем на микросхемах программируемой логики. СПб: БХВ–Петербург, 2002. 608 с.

- 4. Синтез цифровых устройств / Под редакцией Т. Лубы. Варшава: ВКЛ, 2003. 206 с.

- 5. Miller D.M., Maslov D., Dueck G.W. A transformation based algorithm for reversible logic synthesis // Proceedings Design Automation Conference, 2003, pp. 318–323.

- 6. Mo F., Brayton R.K. Whirlpool PLAs: A regular logic structure and their synthesis // IEEE/ACM International Conference on Computer–Aided Design, Digest of Technical Papers, 2002, pp. 543–550.

- 7. Баркалов А. А. Синтез устройств управления на программируемых логических устройствах Донецк: ДонНТУ, 2002. 262 с.

- 8. Баранов С. И. Синтез микропрограммных автоматов. Л.: Машиностроение, 1978. 234 с.

- 9. Баркалов А.А., Палагин А.В. Синтез микропрограммных устройств управления. Киев: ИК НАН Украины, 1997. 136 с.