УДК 681.3

A.A. Баркалов, Е.В. Струнилин, В.Н. Струнилин Донецкий национальный технический университет vstrun@dgtu.donetsk.ua

# Уменьшение емкости управляющей памяти композиционного микропрограммного устройства управления

Предлагается метод уменьшения емкости управляющей памяти в схеме композиционного микропрограммного устройства управления с общей памятью. Метод основан на преобразовании адресов микрокоманд в коды расширенных наборов микроопераций. Предложены три модификации метода, направленные на уменьшение аппаратурных затрат в схеме блока адресации микрокоманд.

**Ключевые слова:** уменьшение емкости управляющей памяти, композиционное микропрограммное устройство управления с общей памятью, преобразование адресов микрокоманд, микрооперация, блок адресации микрокоманд

#### Введение

Практически каждая цифровая система включает в свой состав блок устройства управления (УУ), координирующий взаимодействие остальных блоков системы [1]. При реализации схем УУ возникает задача уменьшения аппаратурных затрат [2,3], решение позволяет уменьшить устройства. Методы решения этой задачи зависят характеристик реализуемого алгоритма управления и особенностей элементного базиса [4]. В настоящей работе рассматривается метод решения этой задачи при реализации схемы УУ по линейной граф - схеме алгоритма (ГСА) с использованием СБИС типа FPGA (fieldprogrammable gate array) [5,6]. В этом случае целесообразно использовать композиционного микропрограммного устройства управления (КМУУ) [4]. Это УУ состоит из блока микрокоманд (БАМ) адресации И управляющей памяти (УП). Известные методы КМУУ, как оптимизации схем ориентированы на уменьшение аппаратных затрат в схеме БАМ [7]. Исключение составляют методы [8,9], что связано с особенностями КМУУ с разделением кодов [7]. В настоящей работе предлагается адаптация этих методов особенностям КМУУ с общей памятью.

Целью исследования является уменьшение управляющей памяти КМУУ за счет введения преобразователя адресов микрокоманд в коды расширенных наборов микроопераций.

Задачей исследования является разработка метода синтеза КМУУ с общей памятью, позволяющего уменьшить число блоков встроенной памяти в схеме УУ. При этом алгоритм управления представляется в виде ГСА [1].

### Основные определения и общие положения

Пусть алгоритм управления цифровой системы представлен в виде ГСА  $\Gamma$ , которая характеризуется множеством вершин  $B = E_1 \cup E_2 \cup \left\{b_0, b_1\right\}$  и дуг E, соединяющих эти вершин. Здесь  $E_1$  — множество операторных вершин, содержащих наборы микроопераций из множества микроопераций (МО)  $Y = \{y_1, ...., y_n\}$ ;  $E_2$  - множество условных вершин, содержащих элементы множества логических условий (ЛУ)  $X = \{x_1, ...., x_1\}$ ;  $b_0$  - начальная вершина;  $b_E$  - конечная вершина  $\Gamma$ CA  $\Gamma$ . Введем ряд определений [7].

соседних вершин существует дуга <  $b_{gi}, b_{gi+1} > \in E$  , где  $i = 1, ..., F_g - 1$  .

Определение 4. Операторные линейные цепи называются псевдоэквивалентными ОЛЦ (ПОЛЦ), если их выходы связаны с входом одной и той же вершины  $\Gamma CA \Gamma$ .

Любая ОЛЦ  $\alpha_g$  имеет произвольное число входов, обозначаемых  $I_g^k$   $(k=1,...,F_g)$  и образующих множество  $I_g$ , и точно один выход, обозначаемый символом  $O_g$  .

<u>Определение 5</u>. Граф-схема алгоритма  $\Gamma$  является линейной  $\Gamma$ CA, если число ее операторных вершин не менее, чем в два раза превосходит число ОЛЦ.

Пусть для ГСА Г получено множество ОЛЦ  $C = \{\alpha_1,...,\alpha_G\}$ , где каждая ОЛЦ  $\alpha_g \in C$  включает максимально возможное число компонент [7]. Пусть  $I(\Gamma)$ ,  $O(\Gamma)$  — соответственно множество входов и выходов ОЛЦ ГСА Г. Каждая вершина  $b_q \in E_1$  соответствует микрокоманде  $MI_q$ , имеющей адрес  $A(b_q)$ . Выполним адресацию микрокоманд так, чтобы выполнялось условие

$$A(b_{qi+1}) = A(b_{qi}) + 1,$$

(1)

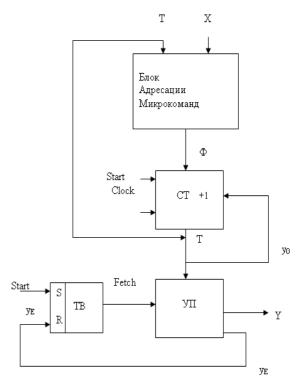

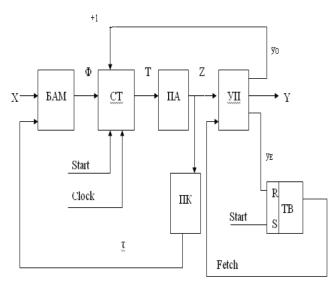

где  $g \in \{1, ..., G\}$ ,  $i \in \{1, ..., F_g - 1\}$ . В этом случае для интерпретации линейной ГСА Г можно использовать модель КМУУ с общей памятью (рис. 1), обозначаемую в дальнейшем символом  $U_1$ . Эта модель включает блок адресации микрокоманд (БАМ), счетчик (СТ), блок УП и триггер выборки (ТВ). Устройство  $U_1$  функционирует следующим образом.

По сигналу Start в СТ записывается нулевой адрес, соответствующий началу микропрограммы, интерпретирующей ГСА  $\Gamma$ , одновременно триггер ТВ устанавливается в единичное состояние (Fetch=1) и микрокоманды могут выбираться из блока УП. Если СТ содержит адрес  $A(b_q)$  и  $b_q \notin O(\Gamma)$ , то одновременно с набором микроопераций  $Y(b_q)$ , записанных в вершине  $b_q \in E_1$ , УП формирует сигнал  $y_0$ . Если  $y_0$ =1, то содержимое СТ увеличивается на единицу по сигналу Clock. При этом выполняется безусловный переход, соответствующий равенству (1). В том случае, если  $b_q \in O(\Gamma)$ , то сигнал  $y_0$  не формируется, а блок БАМ вырабатывает функции возбуждения СТ

$$\Phi = \Phi(T, X) . \tag{2}$$

В этом случае по сигналу Clock в CT формируется адрес перехода из выхода некоторой ОЛЦ  $\alpha_q \in C$ . Если < b $_q$ , b $_E > \in E$  , то блок УП формирует сигнал у $_E$ , вызывающий установку триггера ТВ в нулевое состояние. При этом Fetch = 0, выборка микрокоманд прекращается и КМУУ  $U_1$  прекращает функционирование.

Рисунок 1 — Структурная схема КМУУ  $U_1$

При реализации схем КМУУ U<sub>1</sub> на FPGA схемы БАМ, СТ и ТВ строятся на LUT элементах, а блоки EMB используются для реализации управляющей памяти.

### Основные идеи предлагаемого метода

В управляющей памяти КМУУ  $U_1$  хранится  $M = \left| E_1 \right|$  макрокоманд, каждая из которых соответствует одной вершине  $\mathbf{b}_{\mathbf{q}} \in \mathbf{E}_1$ . Для адресации микрокоманд используется  $\mathbf{R}_{\mathbf{M}}$  адресных разрядов, где

$$R_{\mathbf{M}} = \left| \log_2 \mathbf{M} \right|. \tag{3}$$

Назовем множество  $Y(b_q)\subseteq Y$  микроопераций, записанных в вершине  $b_q\in E_1$ , набором микроопераций (НМО). В УП хранятся расширенные наборы микроопераций (РНМО), включающие МО  $y_n\in Y$  и две дополнительные переменные  $y_0$  и  $y_E$ . Пусть в УП храниться  $M_1$  различных РНМО. Для их кодирования достаточно  $R_1$  двоичных переменных, где

$$R_{\mathbf{I}} = \left| \log_2 M_1 \right|. \tag{4}$$

При выполнении условия

$$R_{I} < R_{M} \tag{5}$$

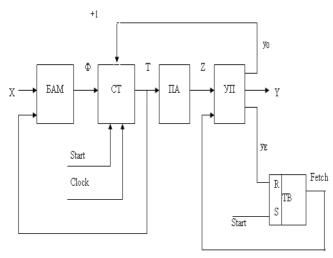

ёмкость УП может быть уменьшена за счет введения преобразователя адреса (ПА) микрокоманды в код РНМО. Это приводит к модели КМУУ  $\rm U_2$  (рис. 2).

Рисунок 2 — Структурная схема КМУУ  $U_2$

Очевидно, принципы функционирования КМУУ  $U_1$  и  $U_2$  совпадают. Разница заключается в том, что в КМУУ  $U_2$  адреса микрокоманд преобразовываются в коды РНМО. Для кодирования РНМО используются переменные  $\mathbf{z}_{_{\mathbf{I}}} \in \mathbf{Z}$ , где  $|\mathbf{Z}| = \mathbf{R}_{_{\mathbf{I}}}$ . В настоящей работе предлагается метод синтеза КМУУ  $U_2$ .

## Метод синтеза КМУУ $U_{\gamma}$

Предлагаемый метод синтеза включает следующие этапы:

- 1. Формирование множества ОЛЦ  $C = \{\alpha_1,...,\alpha_G\} \text{ по } \Gamma CA \Gamma.$

- 2. Построение множества расширенных кадров микроопераций V.

- 3. Если условие (5) выполняется, то синтез КМУУ  $\rm U_2$  продолжается.

- 4. Кодирование PHMO  $\mathbf{v_m} \in \mathbf{V}$  двоичными кодами  $\mathbf{K(v_m)}$  .

- 5. Формирование содержимого управляющей памяти.

- 6. Адресация микрокоманд  ${

m MI}_{

m q}$  использованием (1).

- 7. Построение таблицы переходов КМУУ  $\mathrm{U}_2$ .

- 8. Формирование системы функций (2).

- 9. Формирование таблицы преобразователя адреса.

- 10. Реализация схем блоков КМУУ  $\,{\rm U}_2\,$  в заданном элементном базисе.

Рассмотрим более подробно некоторые из этих этапов. Множество ОЛЦ С формируется с использованием известных методов [7]. Пусть для некоторых ГСА  $\Gamma_1$  имеем  $C = \{\alpha_1, ..., \alpha_{17}\}$  и M=58. Очевидно, эта ГСА является линейной, так как M/G = 58/17 = 3,41 > 2. При этом  $R_{M} = 6, \quad \Phi = \{D_{1}, ..., D_{6}\}$  и  $T = \{T_1, ..., T_6\}.$ Пусть множество V включает  $M_1 = 30$  различных РНМО. Это множество формируется следующим образом. Если вершина  $b_q \in E_1$  не является выходом ОЛЦ  $\alpha_g \in C$  (то есть  $b_q \notin O(\Gamma)$ ), то в набор  $Y(b_q)$  добавляется переменная  $y_0$ . Если  $\mathbf{b}_q \in \mathrm{O}(\Gamma)$  и  $<\mathbf{b}_q, \mathbf{b}_E> \not\in \mathrm{E}$  , то набор  $\mathrm{Y}(\mathbf{b}_q)$  не меняется. В противном случае (<  $b_q$ ,  $b_E$   $>\in E$ ), в набор  $Y(b_{\alpha})$  вводится переменная  $y_E$ . Так как  $M_1 = 30$ , то  $R_1 = 5$ , условие (5) выполняется и синтез КМУУ  $U_2$  имеет смысл.

Пусть код  $K(v_m)$  совпадает с  $R_I$  разрядным двоичным эквивалентом индекса m (  $m=\overline{1,M_1}$  ). В рассматриваемом примере имеем  $K(v_1)=00001,\ K(v_2)=00010$  и так далее. Это позволяет сформировать содержимое УП. Пусть  $v_2=\{y_1,y_3,y_0\}$  , тогда по адресу 00010 будут записаны единицы в столбцах  $y_0,y_1$  и  $y_3$  . Такая процедура выполняется для всех РНМО  $v_m\in V$  .

Адресация микрокоманд (1) выполняется по известной методике [7]. Для формирования таблицы переходов КМУУ  $U_2$  необходимо построить систему формул перехода для вершин  $b_q \in O(\Gamma)$ . Этот этап также выполняется по известной методике [7].

Таблица ПА имеет столбцы  $\,A(b_q^{})\,,\,\,k(v_q^{})\,,$   $\,Z_q^{}$  ,  $\,q$  , где  $\,q=\overline{1,H}\,.$

Пусть для ОЛЦ  $\alpha_6=<$   $\mathbf{b}_6,$   $\mathbf{b}_{16},$   $\mathbf{b}_{17}>$  имеем  $A(b_{15})=001110$ . Тогда, согласно (1), получаем  $A(b_{16})=001111,$   $A(b_{17})=010000$ . Пусть вершине  $\mathbf{b}_{15}\in \mathrm{I}(\Gamma)$  соответствует набор  $\mathbf{v}_6=\{\mathbf{y}_0,\mathbf{y}_7,\mathbf{y}_{11}\},$  вершине  $\mathbf{b}_{16}\in \mathbf{D}^6$  - набор  $\mathbf{v}_{11}=\{\mathbf{y}_0,\mathbf{y}_5,\mathbf{y}_{17}\}$  и вершине  $\mathbf{b}_{17}\in \mathrm{O}(\Gamma)$  - набор  $\mathbf{v}_{18}=\{\mathbf{y}_3,\mathbf{y}_9\}$ . Это приводит к следующему фрагменту таблицы ПА (табл. 1).

Таблица 1. Фрагмент таблицы ПА для КМУУ  $\rm\,U_{2}$

| $A(b_q)$ | k(v <sub>q</sub> ) | $Z_q$       | q  |

|----------|--------------------|-------------|----|

| 001110   | 00110              | $Z_3Z_4$    | 15 |

| 001111   | 01011              | $Z_2Z_4Z_5$ | 16 |

| 010000   | 10010              | $z_1 z_4$   | 17 |

Отметим, что система  $Z \in Z(T)$  может быть реализована либо на блоках EMB, либо на LUT элементах. Последний этап синтеза связан с применением промышленных САПР и выходит за рамки нашей статьи.

### Модификация структуры КМУУ $U_2$

Рассмотренный метод может быть модифицирован так, что бы он позволял уменьшить число LUT элементов в схеме БАМ. Для этого необходимо уменьшить число входов в блоке БАМ. Дальнейшее уменьшение числа LUT возможно при одновременном уменьшении числа входов и термов в функциях  $D_r \in \Phi$ . В настоящей работе предлагаются три подхода к решению этой задачи.

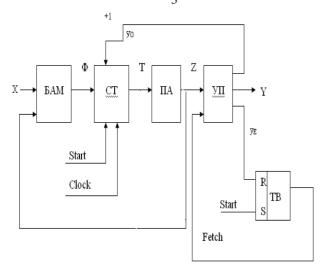

Пусть каждому выходу  $b_q \in O(\Gamma)$  соответствует уникальный РНМО  $v_m \in V$ . При этом ОЛЦ, выход которых связан с входом вершины  $b_E$ , не рассматриваются. В этом случае коды  $K(v_m)$ , соответствующие выходам ОЛЦ, могут рассматриваться как коды выходов ОЛЦ. Это приводит к модели  $U_3$  (рис. 3).

Рисунок 3 – Структурная схема КМУУ  $U_3$  В КМУУ  $U_3$  блок БАМ реализует функции  $\Phi = \Phi(X,Z)$ . (6)

При выполнении (5) система (6) имеет меньше входов, чем система (2). Это приводит к уменьшению числа LUT элементов в схеме БАМ  $\rm U_3$  по сравнению с КМУУ  $\rm U_2$ .

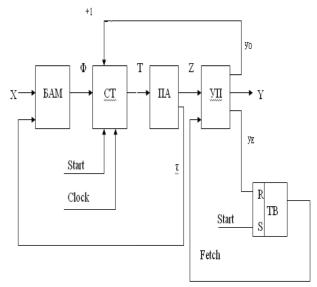

Пусть  $\pi_c = \{B_1,...,B_I\}$  — разбиение множества ОЛЦ С на классы псевдоэквивалентных ОЛЦ. Закодируем каждый класс  $B_i \in \pi_c$  двоичным кодом разрядности  $R_B$ , где

$$R_{\mathbf{B}} = \left| \log_2 I \right|. \tag{7}$$

Используем для кодирования классов  $\mathbf{B_i} \in \pi_{\mathbf{C}}$  переменные  $\tau_r \in \tau$ , где  $|\tau| = \mathbf{R_B}$ . Блок ПА можно использовать для преобразования адресов выходов ОЛЦ  $\alpha_{\mathbf{g}} \in \mathbf{C}$  в коды классов  $\mathbf{B_i} \in \pi_{\mathbf{C}}$ . Это приводит к КМУУ  $\mathbf{U_4}$  (рис. 4).

Рисунок 4 — Структурная схема КМУУ  $U_{\Delta}$

В КМУУ

$$\, {\rm U}_4 \,$$

блок БАМ реализует функции

$$\Phi = \Phi(X,\tau) \, . \eqno(8)$$

Система (8) имеет меньше входов и термов, чем система (2).

Если существуют условия для использования КМУУ  $U_3$ , то функции Z могут быть использованы для реализации преобразователя кодов ПК. Это ведет к КМУУ  $U_5$  (рис. 5).

Рисунок 5 - Структурная схема В КМУУ  $U_{5}$

В КМУУ U<sub>5</sub> блок ПК реализует систему функций

$$\tau = \tau(Z) \ . \tag{9}$$

Применение этого метода имеет смысл, если суммарная сложность блоков ПА и ПК в КМУУ U<sub>5</sub> меньше, чем сложность блока ПА в КМУУ  $U_4$ .

### Заключение

Предлагаемый метод основан преобразовании адресов микрокоманд в расширенных наборов микроопераций.

При выполнении условия (5) метод позволяет уменьшить число встроенных блоков памяти в схеме КМУУ с общей памятью. В КМУУ U<sub>1</sub> требуется управляющая память, имеющая емкость

$$V(U_1) = 2^R M \cdot (N+2)$$

. (10)

В КМУУ  $\,{\rm U}_2\,$  этот параметр уменьшается до

$$V(U_2) = 2^{R_1} \cdot (N+2)$$

. (11)

Однако в КМУУ U2 вводится блок ПА, имеющий емкость

$$W(U_2) = 2^R M \cdot R_I. \tag{12}$$

Применение предлагаемого метода имеет смысл при выполнении условия

$$(V(U_1)/(V(U_2) + W(U_2))) > 1.$$

(13)

$$\begin{split} &(V(U_1)/(V(U_2)+W(U_2)))>1\,. \\ &\text{работе} & \text{также} & \text{предложены} \end{split}$$

три модификации  $U_2$ , модели позволяющие уменьшить сложность схемы блока адресации микрокоманд. Дальнейшие исследования авторов будут направлены на разработку методов синтеза КМУУ  $U_3 - U_5$ , а также исследование области эффективного применения предложенных методов.

Практическая значимость предложенного метода заключается в уменьшении аппаратных затрат в схеме КМУУ с общей памятью по сравнению с известными методами.

### Литература

- 1. Baranov S. Logic and System Design of Digital Systems / S. Baranov.- Tallin: TUT Press, 2008.-266 pp.

- 2. Баркалов А.А. Синтез микропрограммных автоматов на заказных и программируемых СБИС / А.А. Баркалов, Л.А. Титаренко. – Донецк: УНИТЕХ, 2009. – 336 с.

- Соловьев В.В. Логическое проектирование цифровых систем на ПЛИС / В. Соловьев, М.: Горячая линия-Телеком, 2008. – 376 с. А. Климович. -

- DeMicheli G. Synthesis and Optimization of Digital Circuits. McGrow-Hill. 1994. №4. 636 pp.

- 5. Altera Devices [Электронный ресурс]. – Режим доступа: www.altera.com

- 6. Products & Services [Электронный ресурс]. – Режим доступа: www.xilinx.com

- 7. Barkalov A.A. Logic Synthesis for Compositional Microprogram Control Units / A. Barkalov, L. Titarenko. – Berlin: Springer, 2008 – 272 pp.

- Баркалов А.А. Оптимизация схемы композиционного микропрограммного устройства управления с разделением кодов / А.А. Баркалов, Р.В. Мальчева, А.А. Красичков, Халед Баракат // Радиоэлектроника и информатика. – 2006. – №1. – С. 46–50.

- Баркалов А.А. Применение преобразования адресов в КМУУ с разделением кодов / А.А. Баркалов, Р.В. Мальчева, А.А. Красичков, Халед Баракат // Труды седьмой МНПК «Современные информационные и электронные технологии», 22-26 мая 2006 г. – Одесса. – 2006. – С. 182.

Надійшла до редакції 20.02.2011