УДК 004.274

А.А. Баркалов<sup>1</sup>, д-р техн. наук, проф., Р.В. Мальчева<sup>2</sup>, канд. техн. наук, доц., А.А. Баркалов<sup>3</sup>, аспирант <sup>1</sup>Университет Зеленогурский, г. Зелена Гура, Польша <sup>2</sup>Донецкий национальный технический университет, г. Донецк, Украина <sup>3</sup>Институт кибернетики НАН Украины, г. Киев, Украина raisa@cs.dgtu.donetsk.ua

# Реализация схемы автомата Мили в базисе гибридных FPGA

Предложен метод уменьшения аппаратурных затрат в схеме микропрограммного автомата Мили, ориентированный на технологию гибридных FPGA. Метод основан на использовании модели PR-автомата и реализации системы микроопераций на встроенных блоках PLA. Такой подход позволяет уменьшить число LUT элементов в схеме автомата. Приведены условия применения предложенного метода.

Ключевые слова: микропрограммный автомат, PR-автомат, FPGA, LUT, PLA синтез.

#### Введение

Модель микропрограммного автомата (МПА) Мили широко применяется для реализации схем устройств управления [1]. В настоящее время для реализации цифровых систем используется базис программируемых логических интегральных схем типа FPGA (field-programmable gate arrays) [2,3]. Как правило, микросхемы FPGA включают элементы табличного типа, называемые LUT (lookup table), и встроенные блоки памяти ЕМВ (embedded memory blocks) [4,5]. Одной из важных проблем, возникающих при реализации схем МПА в базисе FPGA, является проблема уменьшения цикла LUT элементов [6]. Решение этой задачи позволяет уменьшить число межсоединений в схеме. Это, в свою очередь, приводит к увеличению быстродействия и уменьшению потребления энергии [7].

Одним из путей решения этой проблемы является замена LUT элементов встроенными блоками памяти [3,8]. Однако этот метод применим только для МПА Мура [3]. При синтезе схемы МПА Мили с EMB целесообразно использовать модель PR-автомата [9]. Отметим, что этот подход является эффективным для автоматов средней сложности, в которых разрядность кодов состояний не превышает 6 [1]. В случае сложных автоматов блока EMB должны иметь более 16 входов, что приводит к их крайне неэффективному использованию.

<u>Целью исследований</u> является уменьшение числа LUT элементов в схеме PR-автомата Мили за счет использования блоков PLA для реализации систем микроопераций.

Задачей исследований является адаптация методов синтеза PR-автоматов к особенностям гибридных FPGA.

#### Реализация автомата Мили на FPGA

Схема МПА Мили задается двумя системами функций [1]:

$$\Phi = \Phi(T, X),\tag{1}$$

$$Y = Y(T, X), \tag{2}$$

где  $X = \left\{x_1,...,x_L\right\}$  - множество входных переменных (логических условий);  $Y = \left\{y_1,...,y_N\right\}$  - множество выходных переменных (микроопераций);  $T = \left\{T_1,...,T_R\right\}$  - множество внутренних переменных, кодирующих состояние  $a_m \in A$ , где  $A = \left\{a_1,...,a_M\right\}$  - множество состояний автомата;  $\Phi = \left\{D_1,...,D_R\right\}$  - множество функций возбуждения памяти МПА.

Число переменных

$$T_r \in T$$

определяется:

$$R = \left\lceil \log_2 M \right\rceil. \tag{3}$$

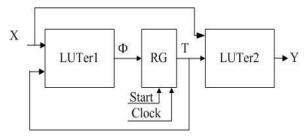

При реализации схем МПА Мили на FPGA системы (1) и (2) реализуются на LUT элементах. Обозначим совокупность LUT элементов символом LUTer, полученная схема МПА Мили приведена на рис.1.

Рисунок 1 - Структурная схема автомата Мили на LUT элементах

В схеме блок LUTer1 реализует систему (1), а блок LUTer2 — систему (2). Регистр RG хранит код  $K(a_m)$  состояния МПА. По сигналу Start в RG записывается нулевой код начального состояния  $a_m \in A$ . По сигналу Clock происходит смена кодов состояния в RG.

При синтезе схем на FPGA производится раздельная минимизация, декомпозиция и реализация каждой функции систем (1) и (2) [12]. При этом блоки схем не имеют общих LUT элементов, что помогает упростить межсоединения.

В работе [9] предложено уменьшить число LUT элементов за счет использования модели PR-автомата [3]. Оптимизация схемы достигается путем замены блока LUTer2 блоком EMBer, состоящим из встроенных блоков памяти. Такой подход позволяет использовать блоки EMB без кодирования наборов микроопераций (HMO)  $Y_t \subseteq Y$ . Анализ стандартных автоматов из библиотеки [13] показал, что EMBer состоит из одного блока EMB для подавляющего числа примеров (87%).

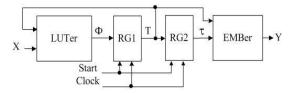

В PR-автомате набор  $Y_t \subseteq Y$  определяется парой состояний  $<a_m$ ,  $a_s>=<$ исходное состояние, состояние перехода> [14]. В работе [9] предложена структурная схема PR-автомата (рис.2). Обозначим автомат, приведенный на рис.1, символом  $U_1$ , а на рис.2 - символом  $U_2$ .

Рисунок 2 - Структурная схема автомата Мили  $U_2$

B автомате  $U_2$  регистр RG1 хранит код  $K(a_m)$  исходного состояния, а регистр RG2 – код  $K(a_s)$  состояния перехода. Для представления кодов в RG2 используются переменные  $\, \tau_r \in \tau \,$  , где По сигналу Start в оба регистра записывается код начального состояния  $a_1 \in A$ . В каждом такте схема LUTer формирует функции (1), определяющие код состояния перехода. По Clock код исходного сигналу переписывается в RG2, а код состояния перехода записывается в RG1. Блок EMBer формирует выходные функции, определяемые следующим образом:

$$Y = Y(T, \tau) . (4)$$

Функционирование продолжается аналогичным образом до записи в RG1 кода состояния  $a_1 \in A$ . Дальнейшая работа МПА возможна только по очередному сигналу Start.

Современные FPGA имеют блоки EBM с конфигурациями  $16K \times 1$ ,  $8K \times 2$ ,  $4K \times 4$ ,  $2K \times 8$ ,  $1K \times 16$ ,  $512 \times 32$  [4,5]. Т.о. число входов варьируется от 14 до 9. Очевидно, что для сложных МПА, у которых R>7, применение модели PR-автомата невозможно. В настоящей работе предлагается заменить блоки EMB блоками PLA, что возможно при использовании гибридных FPGA.

# Реализация PR-автомата в базисе гибридных FPGA

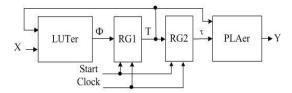

Структурная схема МПА  $U_3$ , предлагаемого в данной работе, практически совпадает со схемой на рис.2, блок EMBer заменен блоком PLAer, состоящим из макроячеек типа PLA (рис.3).

Рисунок 3 - Структурная схема автомата Мили U<sub>3</sub>

Принципы функционирования МПА  $U_2$  и  $U_3$  совпадают. Отметим, что современные гибридные FPGA включают блоки PLA, число входов (S) которых значительно превосходит число входов EMB. Так, в FPGA APEX20K [4] имеются блоки PLA со следующими параметрами: S=32, t=16 и q=32. Здесь t,q — собственно число входов и термов PLA.

В настоящей работе предлагается метод синтеза автомата  $U_3$  по граф-схеме алгоритма (ГСА). Метод включает следующие этапы:

- 1. Формирование множества состояний А.

- 2. Кодирование состояний  $a_m \in A$  .

- 3. Формирование прямой структурной таблицы (ПСТ) автомата Мили.

- 4. Формирование таблицы блока LUTer.

- 5. Формирование таблицы блока PLAer.

- 6. Реализация схемы автомата в заданном базисе.

## Пример синтеза PR-автомата на гибридных FPGA

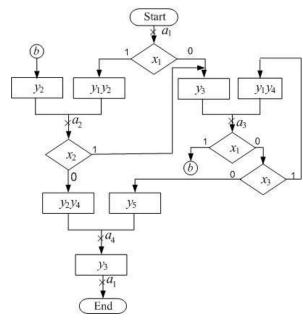

Рассмотрим пример синтеза МПА  $U_3(\Gamma_1)$ , т.е. автомата  $U_3$  на основе граф-схемы алгоритма (ГСА)  $\Gamma_1$  (рис.4.). Исходная ГСА  $\Gamma_1$  отмечена состояниями автомата Мили по правилам [1]. Из рис.4. можно найти следующие множества:  $X = \left\{x_1, x_2, x_3\right\}, Y = \left\{y_1, ..., y_5\right\}, A = \left\{a_1, ..., a_4\right\}$ . T.e, L=3, N=5, M=4.

Используя [3], можно найти R=2,  $T=\left\{T_1,T_2\right\}$ и  $\Phi=\left\{D_1,D_2\right\}$ .

Рисунок 4 - Исходная отмеченная ГСА  $\Gamma_1$

Закодируем состояния автомата  $U_3(\Gamma_1)$  тривиальным образом:  $K(a_1) = 00,...K(a_4) = 11$ .

Построим прямую структурную таблицу автомата  $S_1$ , соответствующего ГСА  $\Gamma_1$  (табл.1).

Таблица блока LUTer строится по исходной ПСТ. Обе таблицы включают H=8 строк.

Для построения таблицы блока LUTer достаточно удалить из исходной ПСТ столбец  $Y_h$ , содержащий наборы  $Y_t \subseteq Y$  (табл.2).

Табл.2 используется для формирования функций (1). Для уменьшения числа LUT элементов каждая из функций  $D_r \in \Phi$  должна быть проминимизирована.

Например, с учетом минимизации из табл.2 можно получить следующее уравнение:

$$D_1 = \overline{T}_1 \overline{T}_2 x_1 \vee \overline{T}_1 T_2 \vee T_1 \overline{T}_2 x_1 = \overline{T}_2 x_1 \vee \overline{T}_1 T_2.$$

Это уравнение может быть реализовано на одном LUT элементе, имеющем не менее трёх входов.

Таблица 1. Прямая структурная таблица автомата  $S_1$

| $a_{\rm m}$ | K(a | $a_{\rm s}$ | K(a <sub>s</sub> | $X_h$                              | $Y_h$                                       | $\Phi_{\rm h}$ | h |

|-------------|-----|-------------|------------------|------------------------------------|---------------------------------------------|----------------|---|

|             | m)  |             | )                |                                    |                                             |                |   |

| $a_1$       | 00  | $a_2$       | 01               | $\mathbf{x}_1$                     | $y_1y_2$                                    | $D_2$          | 1 |

|             |     | $a_3$       | 10               | _<br>X1                            | <b>y</b> <sub>3</sub>                       | $D_1$          | 2 |

| $a_2$       | 01  | $a_3$       | 10               | x <sub>2</sub>                     | у <sub>3</sub>                              | $D_2$          | 3 |

|             |     | $a_4$       | 11               |                                    | <b>y</b> <sub>2</sub> <b>y</b> <sub>4</sub> | $D_1D$         | 4 |

|             |     |             |                  |                                    |                                             | 2              |   |

| $a_3$       | 10  | $a_2$       | 01               | $\mathbf{x}_1$                     | $y_2$                                       | $D_2$          | 5 |

|             |     | $a_3$       | 10               | -<br>x <sub>1</sub> x <sub>3</sub> | y <sub>1</sub> y <sub>4</sub>               | $\mathbf{D}_1$ | 6 |

|             |     | $a_4$       | 11               | <br>X <sub>1</sub> X <sub>3</sub>  | <b>y</b> <sub>5</sub>                       | $D_1D$         | 7 |

| _           | 1.1 | _           | 00               | 1                                  |                                             |                | 0 |

| $a_4$       | 11  | $a_1$       | 00               | 1                                  | <b>y</b> <sub>3</sub>                       | -              | 8 |

Таблица 2. Таблица блока LUTer PR-автомата S<sub>1</sub>

| $a_{\rm m}$       | $K(a_m)$ | $a_{\rm S}$    | $K(a_s)$       | $X_h$                | $\Phi_{\rm h}$ | h |

|-------------------|----------|----------------|----------------|----------------------|----------------|---|

| $a_1$             | 00       | $a_2$          | 01             | $\mathbf{x}_1$       | $D_2$          | 1 |

|                   |          | $a_3$          | 10             | _<br>X1              | $D_1$          | 2 |

| a <sub>2</sub> 01 | $a_3$    | 10             | x <sub>2</sub> | $D_1$                | 3              |   |

|                   | 01       | $a_4$          | 11             | _<br>X2              | $D_1D_2$       | 4 |

|                   |          | $\mathbf{a}_2$ | 01             | $\mathbf{x}_1$       | $D_2$          | 5 |

| a <sub>3</sub>    | 10       | $a_3$          | 10             | $\overline{x}_1 x_2$ | $D_1$          | 6 |

|                   |          | $a_4$          | 11             | <br>X1 X2            | $D_2D_1$       | 7 |

| $a_4$             | 11       | $a_1$          | 00             | 1                    |                | 8 |

Для построения таблицы блока PLAer необходимо удалить из исходной ПСТ столбцы

$X_h$  и  $\Phi_h$ . Это дает следующую промежуточную таблицу (табл.3).

Таблица 3. Промежуточная таблица PR-автомата S<sub>1</sub>

| $a_{\rm m}$           | K(a <sub>m</sub> ) | $a_{S}$ | K(a <sub>s</sub> ) | $Y_h$                                       | h |

|-----------------------|--------------------|---------|--------------------|---------------------------------------------|---|

| 0                     | 00                 | $a_2$   | 01                 | <b>y</b> <sub>1</sub> <b>y</b> <sub>2</sub> | 1 |

| $\mathbf{a}_1$        | 00                 | $a_3$   | 10                 | $y_3$                                       | 2 |

| $a_2$                 | 01                 | $a_3$   | 10                 | <b>y</b> <sub>3</sub>                       | 3 |

| <b>u</b> <sub>2</sub> | 01                 | $a_4$   | 11                 | $y_{2}y_{4}$                                | 4 |

|                       |                    | $a_2$   | 01                 | $\mathbf{y}_2$                              | 5 |

| $a_3$                 | 10                 | $a_3$   | 10                 | <b>y</b> <sub>1</sub> <b>y</b> <sub>4</sub> | 6 |

|                       |                    | $a_4$   | 11                 | <b>y</b> 5                                  | 7 |

| $a_4$                 | 11                 | $a_1$   | 00                 | <b>y</b> <sub>3</sub> <b>y</b> <sub>4</sub> | 8 |

Таблица блока PLAer имеет H=8 строк (табл.4.) Отметим, что в случае PR-автомата с блоком EMDer [9] соответствующая таблица имеет 16 строк.

Таблица 4. Таблица блока PLAer автомата  $U_3(\Gamma_1)$

| K(a <sub>s</sub> ) |          | K(a <sub>m</sub> ) |       | Y              |                |                |       |       |   |

|--------------------|----------|--------------------|-------|----------------|----------------|----------------|-------|-------|---|

| $\tau_1$           | $\tau_2$ | $T_1$              | $T_2$ | $\mathbf{Y}_1$ | $\mathbf{Y}_2$ | $\mathbf{Y}_3$ | $Y_4$ | $Y_5$ | h |

| 0                  | 1        | 0                  | 0     | 1              | 1              | 0              | 0     | 0     | 1 |

| 1                  | 0        | 0                  | 0     | 0              | 0              | 1              | 0     | 0     | 2 |

| 1                  | 0        | 0                  | 1     | 0              | 0              | 1              | 0     | 0     | 3 |

| 1                  | 1        | 0                  | 1     | 0              | 1              | 0              | 1     | 0     | 4 |

| 0                  | 1        | 1                  | 0     | 0              | 1              | 0              | 0     | 0     | 5 |

| 1                  | 0        | 1                  | 0     | 1              | 0              | 0              | 1     | 0     | 6 |

| 1                  | 1        | 1                  | 0     | 0              | 0              | 0              | 0     | 1     | 7 |

| 0                  | 0        | 1                  | 1     | 0              | 0              | 1              | 1     | 0     | 8 |

Эта таблица отображает состояния регистров  $RG_1$  и  $RG_2$  после осуществления перехода  $<\!a_m,a_s>$ . При этом регистр  $RG_1$  содержит код состояния перехода  $a_s\in A$ , а регистр  $RG_2$ —код исходного состояния  $a_m\in A$ .

Последний этап предложенного метода связан с построением VHDL-моделей устройство управления и использованием стандартных потоков автоматизированного синтеза [5,6]. В данной статье этот этап не рассматривается.

Рассмотрим условия, при которых использование блоков PLA имеет смысл. Сравним между собой блоки EMBer и PLAer. Как уже отмечалось, конфигурация блоков EMB меняется. Такие блоки имеют постоянную емкость  $V_0$  для различного числа ячеек V и выходов  $t_{\rm F}$ :

$$V_0 = V \cdot t_F. \tag{5}$$

Число ячеек в блоке EMB определяется из выражения (5). Число выходов  $t_F$  может принимать некоторые фиксированные значения, образующие множество O [5,6]. Как уже отмечалось, O= $\{1, 2, 4, 8, 16, 32\}$ .

Параметр  $t_F$  можно определить как ближайший элемент из множества O, удовлетворяющий условию

$$t_{F} \ge \left\lceil \frac{V_{0}}{4^{R}} \right\rceil. \tag{6}$$

После определения величины  $t_F$  можно найти число блоков EMB, необходимое для реализации схемы блока EMBer:

$$n_1 = \left\lceil \frac{N}{t_F} \right\rceil. \tag{7}$$

Аналогичным образом можно найти число  $n_2$  блоков PLA, требуемых для реализации блока PLAer. При выполнении условия  $n_1 > n_2$  выбирается МПА  $U_3$ . В противном случае целесообразно применять МПА  $U_2$ .

#### Заключение

Предложенный метод реализации автомата Мили позволяет уменьшить число LUT элементов в схеме. Метод основан на применении модели PR-автомата и замене части LUT элементов схемой, содержащей блоки PLA. Основной особенностью PR-автомата является устранение непосредственной зависимости между входами (логическими условиями) и выходами (наборами микроопераций) автомата. Такой подход позволяет представить выходные функции в виде таблиц, реализуемых с использованием блоков PLA. В качестве примера авторами рассмотрен контроллер из работы [7]. Данный автомат имеет 172 состояния (R=8) и 26 выходных сигналов. Для данного контроллера применение метода U<sub>2</sub> невозможно, т.к. 2R=16, что превышает число входов современных ЕМВ. При этом схема блока PLAer требует применения всего двух блоков PLA (для FPGA APEX20K). Сравнение схем МПА  $U_1$  и  $U_3$  показало, что схема МΠА U<sub>3</sub> требует на 32% меньше LUT элементов. Таким образом, предложенный метод имеет смысл для сложных автоматов.

Научная новизна предложенного метода заключается в адаптации метода синтеза PR-автомата к особенностям базиса гибридных FPGA. Практическая значимость метода заключается в уменьшении LUT элементов в схеме МПА по сравнению с известными из литературы аналогами.

Дальнейшее направление работы связано с разработкой метода кодирования состояний, позволяющего уменьшить число LUT элементов в схеме формирования функций возбуждения памяти PR-автомата Мили.

#### Список литературы

- 1. Baranov S. Logic and System Design of Digital Systems. Tallinn: TUT Press, 2008. 312 pp.

- 2. Grout I. Digital Systems Design with FPGAs and CPLDs. Amsterdam: Elsevier, 2008.–406 pp.

- 3. Barkalov A., Titarenko L. Logic Synthesis for FSM based Control Units. Berlin: Springer, 2009. 233 pp.

- 4. <a href="http://www.altera.com">http://www.altera.com</a>

- 5. <a href="http://www.xilinx.com">http://www.xilinx.com</a>

- 6. Sklyarov V. Reconfigurable models of fincte state machines and their implementation in FPGAs // Journal of System Architecture. 2002, V.47, №2. P. 1043-1064.

- 7. Czerwinski R., Kania D. Finite state machine logic synthesis for Complex Programmable Logic Devices. Berlin: Springer, 2013. 172 pp.

- 8. Skliarova I., Sklyarov V., Sudnitson A. Design of FPGA-based circuits using Hierarchical Finite State Machines. Tallinn: TTU Press, 2012. 240 pp.

- 9. Баркалов А.А. Уменьшение числа LUT элементов в схеме автомата Мили / А.А. Баркалов, Р.В. Мальчева, А.А. Баркалов // Наукові праці Донецького національного технічного університету. Серія: «Обчислювальна техніка та автоматизація». 2013. № 1(25). С. 168-174.

- 10. Kaviani A., Brown S. The Hybrid Field Programmable Architecture // IEEE Design & Test of Computres. − 1999, V.16, №4. − P. 74-83.

- 11. Singh S., Singh R., Bhatia M. Performance Evaluation of Hybrid Reconfigurable Computing Architecture // International Journal of Embedde Systems and Applications. −2012, V.2, №3. − pp. 107-116.

- 12. Scholl C. Function Decomposition with Application to FPGA Synthesis. Norwell: Kluwer Academic Publishers, 2001. 418 pp.

- 13. Yang S. Logic Synthesis and Optimization Benchmarks User Guide. Technical Report. Microelectronic Center of North Carolina, 1991. 44 pp.

- 14. Баркалов А.А. Оптимизация логической схемы автомата Мили на ПЛМ / А.А. Баркалов, Д.К. Дас // Автоматика и вычислительная техника. 1992. №3. С. 90-94.

Надійшла до редакції 15.03.2014

# O.O. БАРКАЛОВ<sup>1</sup>, Р.В. МАЛЬЧЕВА<sup>2</sup>, O.O. БАРКАЛОВ<sup>3</sup>

<sup>1</sup>Зеленогурський університет, <sup>2</sup>Донецький національний технічний університет, <sup>3</sup>Інститут кібернетики НАН України

### РЕАЛІЗАЦІЯ СХЕМИ АВТОМАТА МІЛІ У БАЗІСІ ГІБРІДНИХ FPGA

Запропонований метод зменшения апаратурних витрат у схемі мікропрограмного автомата Міли, який орієнтирований на технологію гібрідних FPGA. Метод заснований на використанні моделі PR-автомата й реалізації системи мікрооперацій на вбудованих блоках PLA. Такій підход дозволяє зменшити кількість LUT елементів у схемі автомата. Наведені умови застосування запропонованого метода. Виконаний аналіз реализації системи мікрооперацій с використанням блоків PLA і EMB, имеющих конфигурацию 1К×16 (біт), для стандартних автоматів.

Ключові слова: мікропрограмний автомат, PR-автомат, FPGA, LUT, EMB, PLA, синтез.

## A.A. BARKALOV<sup>1</sup>, R.V. MALCHEVA<sup>2</sup>, A.A. BARKALOV<sup>3</sup>

<sup>1</sup>University of Zielona Gora, <sup>2</sup>Donetsk National Technical University, <sup>3</sup>Institute of Cybernetics

# IMPLEMENTING CIRCUIT OF MEALY FSM WITH HINRID FPGAS

The model of Mealy finite state machine (FSM) is widely used for implementing the control units. Nowadays, the hybrid field - programmable gate arrays (HFPGA) are applied for implementing complex digital systems. FPGA have the benefits of the hardware speed and the software flexibility. The last decade has seen ever increasing application areas for FPGAs. Modern FPGAs currently accommodate more than ten million gates with clock rates up to 600 MHz. As a rule, the FPGAs include look-up table (LUT) elements and embedded PLA blocks (programmable logic array). One of the important problems connected with FSM design is the reduction of the number of LUTs in an FSM's logic circuit. The solution of this problem allows decreasing of the number of interconnections among the LUTs. In turn, it leads to increasing of the performance and decreasing of the power dissipation. Using PLAs instead of LUTs is one of the possible ways for solving this problem. In the case of Mealy FSM, the system of microoperations could be implemented with PLAs. But it leads to the encoding of collections of microoperations and using some resources of a chip for generating these additional variables. A method is proposed for reducing the hardware amount in logic circuit of Mealy FSM. The method targets the technology of HFPGA. The method is based on using the model of PR-automaton and implementing the system of microoperations with embedded PLAs. This approach allows reducing the number of LUTs in the FSM's circuit. The conditions are shown for using the proposed method. The example of FSM synthesis is given with applying the proposed approach. An application of proposed method allows the average decrease for the number of LUTs up to 32%. The scientific novelty of the proposed method is reduced to adaptation of the design method for PRautomaton to the specifics of HFPGAs. The practical meaning of the method is determined by reducing for the number of LUTs in an FSM logic circuit in comparison with known methods. The further direction of the research is connected with development of state assignment methods leading to decreasing of the number of LUTs in the circuit of LUTer.

Keywords: finite-state-machine, PR-automaton, HFPGA, LUT, PLA, synthesis.