KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

# Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2012)

Copyright © 2012 by the Institute of Electrical and Electronics Engineers, Inc.

Technically Co-Sponsored by

tttc

Kharkov, Ukraine, September 14 – 17, 2012

#### **TTTC Officers for 2012**

Chair 1st Vice Chair 2nd Vice Chair President of Board Past Chair Senior Past Chair IEEE Design & Test EIC ITC General Chair Test Week Coordinator Secretary Vice Secretary Finance Chair Finance Vice-Chair

#### Group Chairs

**Technical Meetings** Technical Activities Tutorials & Education Standards Communications Standing Committees Industry Advisory Board Electronic Media Asia & Pacific Europe Latin America North America Middle East & Africa

#### **Technical Activity Committees**

Board Testing Defect Tolerance Economics of Test

Embedded Core Test FPGA Testing Freeware libraries IEEE 1149.1 IDDQ Testing Infrastructure IP Memory Testing MEMs Testing

Mixed-Signal Testing Nanometer Testing Nanotechnology Test Network-On-Chip Test **On-Line Testing** Power-Aware Testing RF Testing Silicon Debug and Diagnosis System Test 3D chips & SiP Testing Test Compression Test & Verification Test Education Test Synthesis Thermal Testing

Michael NICOLAIDIS TIMA Laboratory - France Cecilia METRA U. of Bologna - Italy Rohit KAPUR Synopsys, Inc. - USA Yervant ZORIAN Synopsys Inc. - USA Adit D. SINGH Auburn Univ. - USA André IVANOV U. of British Columbia - Canada Krish Chakrabarty Duke U - USA Ron PRESS Mentor Graphics - USA Yervant ZORIAN Synopsys Inc. - USA Joan Figueras UPC Barcelona Tech - Spain Adam OSSEIRAN Edith Cowan U. - Australia Chen-Huan CHIANG Alcatel-Lucent - USA Don WHEATER IBM Microelectronics - USA

Chen-Huan CHIANG Alcatel-Lucent- USA Patrick Girard LIRMM - France Dimitris GIZOPOULOS University of Piraeus - Greece Rohit KAPUR Synopsys, Inc. - USA Cecilia METRA U. of Bologna - Italy André IVANOV U. of British Columbia - Canada Yervant ZORIAN Virage Logic Corp. - USA Giorgio DI NATALE LIRMM - France Kazumi HATAYAMA STARC - Japan Matteo SONZA REORDA Politecnico di Torino - Italy Victor Hugo CHAMPAC Inst. Natl. de Astrofisica - Mexico André IVANOV U. of British Columbia - Canada Ibrahim HAJJ American U. of Beirut - Lebanon

Bill EKLOW Cisco Systems - USA Vincenzo PIURI Politecnico di Milano - Italy Magdy S. ABADIR Freescale, Inc. - USA Anthony P. AMBLER U. of Texas at Austin - USA Yervant ZORIAN Virage Logic Corp. - USA Michel RENOVELL LIRMM - France Burnell WEST NPTest - USA Hardware Security and Trust Jim PLUSQUELLIC University of New Mexico- USA Christopher J. CLARK Intellitech Corporation - USA Manoj SACHDEV University of Waterloo - CA Yervant ZORIAN Virage Logic Corp. - USA Rochit RAJSUMAN Advantest - USA Ronald D. BLANTON Carnegie-Mellon U. - USA Bernard COURTOIS TIMA - France Bozena KAMINSKA IMS Pultronics, Inc. - USA Jaume SEGURA U. of the Balearic Islands - Spain Fabrizio LOMBARDI Northeastern U. - USA Erik Jan MARINISSEN IMEC - Belgium Michael NICOLAIDIS iRoC Technologies - France Patrick GIRARD LIRMM - France Iboun Taimiya SYLLA Texas Instruments - USA Michael RICHETTI ATI Research, Inc. - USA Ian HARRIS UC Irvine - USA Yervant ZORIAN Virage Logic Corp. - USA Rohit KAPUR Synopsys, Inc. - USA Magdy S. ABADIR Freescale, Inc. - USA Sule OZEV Duke U. - USA Scott DAVIDSON Sun Microsystems - USA Bernard COURTOIS TIMA - France

michael.nicolaidis@imag.fr cmetra@deis.unibo.it rkapur@synopsys.com yervant.zorian@synopsis.com adsingh@eng.auburn.edu ivanov@ece.ubc.ca krish@ee.duke.edu ron press@mentor.com yervant.zorian@synopsis.com figueras@eel.upc.edu a.osseiran@ecu.edu.au chen-huan.chiang@alcatel-lucent.com dwheater@us.ibm.com

chen-huan.chiang@alcatel-lucent.com patrick.girard@lirmm.fr dqizop@unipi.gr rkapur@synopsys.com cmetra@deis.unibo.it ivanov@ece.ubc.ca zorian@viragelogic.com giorgio.dinatale@lirmm.fr hatayama.kazumi@starc.or.jp matteo.sonzareorda@polito.it champac@inaoep.mx ivanov@ece.ubc.ca ihajj@aub.edu.lb

ben@dft.co.uk piuri@elet.polimi.it m.abadir@freescale.com ambler@ece.utexas.edu zorian@viragelogic.com renovell@lirmm.fr west@ieee.org jimp@ece.unm.edu cclark@intellitech.com msachdev@ece.uwaterloo.ca zorian@viragelogic.com r.rajsuman@advantest.com blanton@ece.cmu.edu bernard.courtois@imag.fr bozena@pultronics.com dfsjsf4@clust.uib.es lombardi@ece.neu.edu erik.jan.marinissen@imec.be michael.nicolaidis@iroctech.com girard@lirmm.fr isylla@ti.com mike\_ricchetti@ieee.org harris@ics.uci.edu zorian@viragelogic.com rkapur@synopsys.com m.abadir@freescale.com sule@ee.duke.edu scott.davidson@eng.sun.com bernard.courtois@imag.fr

bambang\_suparjo@mentor.com beklow@cisco.com roshana@ti.com gmaston@synopsys.com t.taylor@ieee.org gwilder@ti.com

#### Standards Working Groups

IEEE 1149.4 IEEE 1149.6 IEEE P1149.7 IEEE 1450-1999 IEEE 1450.1 IEEE 1450.2-2002 Bambang SUPARJO Mentor Graphics - USA Bill EKLOW Cisco Systems, Inc. - USA Robert OSHANA Texas Instruments - USA Gregory MASTON Synopsys, Inc. - USA Tony TAYLOR Gregg WILDER Texas Instruments - USA

| IEEE P1450.3     | Tony TAYLOR                                      | t  |

|------------------|--------------------------------------------------|----|

| IEEE P1450.4     | Doug SPRAGUE IBM - USA                           | С  |

|                  | Jim O'REILLY Analog Devices - USA                | ji |

| IEEE P1450.6-1   | Bruce CORY NVIDIA – USA                          | b  |

| IEEE P1450.6-2   | Saman ADHAM LogicVision, Inc Canada              | S  |

| IEEE 1450.6-2005 | Rohit KAPUR Synopsys, Inc USA                    | r  |

| IEEE P1450.7     | Jean-Louis CARBONERO STMicroelectronics - France | je |

| IEEE 1500        | Yervant ZORIAN Virage Logic Corp USA             | Z  |

| IEEE 1532        | Neil JACOBSON Xilinx Corp USA                    | r  |

| IEEE P1581       | Heiko EHRENBERG GOEPEL Electronics - USA         | ł  |

| IEEE P1687       | Kenneth POSSE AMD - USA                          | k  |

|                  | Alfred CROUCH Asset InterTech - USA              | а  |

| IEEE P1838       | Erik Jan MARINISSEN IMEC - Belgium               | e  |

|                  |                                                  |    |

t.taylor@ieee.org dsprague@us.ibm.com jim\_oreilly@ieee.org bcory@nvidia.com saman@logicvision.com rkapur@synopsys.com jean-louis.carbonero@st.com zorian@viragelogic.com neil.jacobson@xilinx.com h.ehrenberg@goepel.com kepos@comcast.net al.crouch@asset-intertech.com erik.jan.marinissen@imec.be

# TTTC-Sponsored Technical Meetings in 2012

| TTTC-Spo            | nsored Technical Meetings in 2012                                                                                                                                           |                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| For the mo          | ost current information, please visit the TTTC website ( <u>http://tab.computer.c</u>                                                                                       | org/tttc)                             |

| or TTTC E           | vents website (http://www.tttc-events.org)                                                                                                                                  |                                       |

| 3/12-3/16           | Design, Automation and Test in Europe (DATE), Dresden, Germany                                                                                                              | W. Rosenstiel                         |

| 3/27-3/28           | Workshop on Silicon Errors in Logic - System Effects (SELSE), U. of Illinois, IL, USA                                                                                       | A. Wood, R. Kumar                     |

| 4/10-4/13           | Latin American Test Workshop (LATW), Quito, Ecuador                                                                                                                         | V. Champac, Y. Zorian                 |

| 4/18-4/20           | Design & Diagnosis of Electronic Circuits & Systems Symposium (DDECS), Tallinn, Estonia                                                                                     | J. Raik                               |

| 4/23-4/26           | VLSI Test Symposium (VTS), Maui, Hawaii, USA                                                                                                                                | C. Metra                              |

| 5/14-5/16           | Int'l Mixed-Signals, Sensors, and Systems Test Workshop (IMS3TW), Taipei, Taiwan, ROC                                                                                       | CW. Wu                                |

| 5/28-6/1            | European Test Symposium (ETS), Annecy, France                                                                                                                               | L. Anghel                             |

| 5/31-6/1            | Int'l Workshop on Impact of Low Power Design on Test and Reliability (LPonTR), Annecy, France                                                                               | A. Bystrow, P. Girard                 |

| 5/31-6/1<br>6/3-6/4 | Int'l Workshop on Processor Verification, Test and Debug (IWPVTD), Annecy, France<br>Int'l Symposium on Hardware-Oriented Security and Trust (HOST), San Francisco, CA, USA | R. Aitken, E. Larsson,V. Singh K. Mai |

| 6/4                 | Int'l Workshop on Design for Manufacturability & Yield (DfM&Y), San Francisco, CA, USA                                                                                      | R. Aitken, Nagaraj NS                 |

| 6/27-6/29           | International On-Line Testing Symposium (IOLTS), Sitges, Spain                                                                                                              | M. Nicolaidis                         |

| 7/12-7/13           | ATE: Vision 2020, San Francisco, CA, USA                                                                                                                                    | E. Volkerink                          |

| 9/11-9/13           | Board Test Workshop (BTW), Fort Collins, CO, USA                                                                                                                            | W. Eklow                              |

| 9/14-9/17           | East-West Design and Test Symposium (EWDTS), Kharkov, Ukraine                                                                                                               | V. Hahanov, Y. Zorian                 |

| 10/3-10/5           | Int'I Symp. on Defect & Fault Tolerance in VLSI and Nanotechnolohy Systems (DFT), Austin, TX, USA                                                                           | P.D. Joshi, M. Violante               |

| 11/5-11/8           | International Test Conference (ITC), Anaheim, CA, USA                                                                                                                       | D. Young                              |

| 11/8-11/9           | Wkshop. on Testing Three-Dimensional Stacked Integrated Circuits (3D-Test), Anaheim, CA, USA                                                                                | Y. Zorian                             |

| 11/8-11/9           | Int'l Defect and Adaptive Testing Workshop (DAT), Anaheim, CA, USA                                                                                                          | S. Menon                              |

| 11/8-11/9           | International Silicon Debug and Diagnosis Workshop (SDD), Anaheim, CA, USA                                                                                                  | T. McLaurin                           |

| 11/9-11/10          | Int'l High Level Design Validation & Test Workshop (HLDVT), Huntington Beach, CA, USA                                                                                       | P. Varma                              |

| 11/19-11/22         | Asian Test Symposium (ATS), Niigata, Japan                                                                                                                                  | K. Hatayama                           |

| 11/22-11/23         | Workshop on RTL and High Level Testing (WRTLT), Niigata, Japan                                                                                                              | M. Hashizume                          |

| 12/TBD              | International Workshop on Microprocessor Test and Verification (MTV), Austin, TX, USA                                                                                       | M. Abadir                             |

| TBD                 | Wkshop. on Test & Validation of High Speed Analog Circuits (TVHSAC), TBD                                                                                                    | TBD                                   |

| TBD                 | Int'l Workshop on Testing Embedded and Core-Based System-Chips (TECS), Online                                                                                               | Y. Zorian                             |

| TBD                 | International Workshop on Design & Test (IDT), TBD                                                                                                                          | Y. Zorian, TBD                        |

|                     |                                                                                                                                                                             |                                       |

# TTTC Office

1 Marsh Elder Lane Savannah, GA 31411 USA Phone: +1-540-937-5066 Fax: +1-540-937-7848 E-mail: tttc@computer.org

# http://tab.computer.org/tttc

# IEEE EAST-WEST DESIGN AND TEST SYMPOSIUM 2012 COMMITTEE

#### General Chairs

V. Hahanov – Ukraine Y. Zorian – USA

#### **General Vice-Chairs**

R. Ubar - Estonia P. Prinetto - Italy

#### **Program Chairs**

S. Shoukourian – Armenia D. Speranskiy – Russia

#### **Program Vice-Chairs**

Z. Navabi – Iran M. Renovell – France

#### **Publicity Chair's**

G. Markosyan - Armenia S. Mosin - Russia

Public Relation Chair

V. Djigan - Russia

#### Program Committee

E. J. Aas - Norway J. Abraham - USA M. Adamski - Poland A.E.Mohamed Mohamed - Egypt A . Barkalov - Poland R. Bazylevych - Ukraine A. Chaterjee - USA V. Djigan - Russia A. Drozd - Ukraine E. Evdokimov - Ukraine E. Gramatova - Slovakia A. Ivanov - Canada M. Karavay - Russia V. Kharchenko - Ukraine K. Kuchukjan - Armenia W. Kuzmicz - Poland A. Matrosova - Russia V. Melikyan - Armenia L. Miklea - Romania O. Novak - Czech Republic Z. Peng - Sweden A. Petrenko - Ukraine J. Raik - Estonia A. Romankevich - Ukraine A. Ryjov - Russia R. Seinauskas - Lithuania S. Sharshunov - Russia A. Singh - USA J. Skobtsov - Ukraine V. Tverdokhlebov - Russia V. Vardanian - Armenia V. Yarmolik - Byelorussia

#### **Steering Committee**

M. Bondarenko - Ukraine

- V. Hahanov Ukraine

- R. Ubar Estonia

- Y. Zorian USA

### **Organizing Committee**

S. Chumachenko - Ukraine

- E. Litvinova Ukraine

- V. Kharchenko Ukraine

## **EWDTS 2012 CONTACT INFORMATION**

Prof. Vladimir Hahanov Design Automation Department Kharkov National University of Radio Electronics, 14 Lenin ave, Kharkov, 61166, Ukraine.

Tel.: +380 (57)-702-13-26 E-mail: hahanov@kture.kharkov.ua Web: www.ewdtest.com/conf/

# 10<sup>th</sup> IEEE EAST-WEST DESIGN & TEST SYMPOSIUM (EWDTS 2012) Kharkov, Ukraine, September 14-17, 2012

The main target of the **IEEE East-West Design & Test Symposium** (EWDTS) is to exchange experiences between scientists and technologies of Eastern and Western Europe, as well as North America and other parts of the world, in the field of design, design automation and test of electronic circuits and systems. The symposium is typically held in countries around the Black Sea, the Baltic Sea and Central Asia region. We cordially invite you to participate and submit your contributions to EWDTS'12 which covers (but is not limited to) the following topics:

- Analog, Mixed-Signal and RF Test

- Analysis and Optimization

- ATPG and High-Level Test

- Built-In Self Test

- Debug and Diagnosis

- Defect/Fault Tolerance and Reliability

- Design for Testability

- Design Verification and Validation

- EDA Tools for Design and Test

- Embedded Software Performance

- Failure Analysis, Defect and Fault

- FPGA Test

- HDL in test and test languages

- High-level Synthesis

- High-Performance Networks and Systems on a Chip

- Low-power Design

- Memory and Processor Test

- Modeling & Fault Simulation

- Network-on-Chip Design & Test

- Modeling and Synthesis of Embedded Systems

- · Object-Oriented System Specification and Design

- On-Line Testing

- Power Issues in Design & Test

- Real Time Embedded Systems

- Reliability of Digital Systems

- Scan-Based Techniques

- Self-Repair and Reconfigurable Architectures

- Signal and Information Processing in Radio and Communication Engineering

- System Level Modeling, Simulation & Test Generation

- System-in-Package and 3D Design & Test

- Using UML for Embedded System Specification

- CAD and EDA Tools, Methods and Algorithms

- Design and Process Engineering

- Logic, Schematic and System Synthesis

- Place and Route

- Thermal, Timing and Electrostatic Analysis of SoCs and Systems on Board

- Wireless and RFID Systems Synthesis

- Digital Satellite Television

The Symposium will take place in Kharkov, Ukraine, one of the biggest scientific and industrial center. Venue of EWDTS 2012 is Kharkov National University of Radioelectronics was founded 81 years ago. It was one of the best University of Soviet Union during 60th - 90th in the field of Radioelectronics. Today University is the leader among technical universities in Ukraine.

The symposium is organized by Kharkov National University of Radio Electronics and Science of Academy Applied Radio Electronics http://anpre.org.ua/ in cooperation with Tallinn University of Technology. It is technically cosponsored by the IEEE Computer Society Test Technology Technical Council (TTTC) and financially supported by Trades Committee of Kharkov National University of Radioelectronics and Trades Committee of Students, Aldec, Synopsys, Kaspersky Lab, DataArt Lab, Tallinn Technical University.

### CONTENTS

| An Efficient Fault Diagnosis and Localization Algorithm for<br>Successive-Approximation Analog to Digital Converters<br>Melkumyan T., Harutyunyan G., Shoukourian S., Vardanian V., Zorian Y.                               | 15 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Application of Defect Injection Flow for Fault Validation in Memories<br>Amirkhanyan K., Davtyan A., Harutyunyan G., Melkumyan T., Shoukourian S.,<br>Vardanian V., Zorian Y.                                               | 19 |

| SSBDDs and Double Topology for Multiple Fault Reasoning<br>Raimund Ubar, Sergei Kostin, Jaan Raik                                                                                                                           | 23 |

| Self Compensating Low Noise Low Power PLL design<br>Vazgen Melikyan, Armen Durgaryan, Ararat Khachatryan, Manukyan Hayk,<br>Eduard Musaelyan                                                                                | 29 |

| Optimization Considerations in QCA Designs<br>Zahra NajafiHaghi, Marzieh Mohammadi, Behjat Forouzandeh, Zainalabedin Navabi                                                                                                 | 33 |

| Implementation of Address-Based Data Sorting on Different FPGA Platforms<br>Dmitri Mihhailov, Alexander Sudnitson, Valery Sklyarov, Iouliia Skliarova                                                                       | 38 |

| Comparison of Model-Based Error Localization Algorithms for C Designs<br>Urmas Repinski, Jaan Raik                                                                                                                          | 42 |

| Synthesis of Clock Trees for Sampled-Data Analog IC Blocks<br>Bilgiday Yuce, Seyrani Korkmaz, Vahap Baris Esen, Fatih Temizkan, Cihan Tunc,<br>Gokhan Guner, I. Faik Baskaya, Iskender Agi, Gunhan Dundar, H. Fatih Ugurdag | 46 |

| Experiences on the road from EDA Developer to Designer to Educator<br>H. Fatih Ugurdag                                                                                                                                      | 50 |

| Multi-Beam Constant Modulus Adaptive Arrays in Real-Valued Arithmetic Victor I. Djigan                                                                                                                                      | 54 |

| Simulation of Total Dose Influence on Analog-Digital SOI/SOS CMOS<br>Circuits with EKV-RAD macromodel<br>Petrosyants K. O., Kharitonov I. A., Sambursky L. M.,<br>Bogatyrev V. N., Povarnitcyna Z. M., Drozdenko E. S.      | 60 |

| Models for Embedded Repairing Logic Blocks<br>Hahanov V.I., Litvinova E.I., Frolov A., Tiecoura Yves                                                                                                                        | 66 |

| Real-time Interconnection Network for Single-Chip Many-Core Computers<br>Harald Richter                                                                                                                                     | 72 |

| Invariant-Oriented Verification of HDL-Based Safety Critical Systems<br>Kharchenko V., Konorev B., Sklyar V., Reva L.                                                                                                       | 76 |

| An Improved Scheme for Pre-computed Patterns in Core-based SoC Architecture<br>Elahe Sadredini, Qolamreza Rahimi, Paniz Foroutan,<br>Mahmood Fathy, Zainalabedin Navabi                                                     | 80 |

| Synthesis of Moore FSM with transformation of system in CPLD<br>Aleksander Barkalov, Larysa Titarenko, and Sławomir Chmielewski                                                                                                                                                      | 85  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A WSN Approach to Unmanned Aerial Surveillance of Traffic Anomalies:<br>Some Challenges and Potential Solutions<br>David Afolabi, Ka Lok Man, Hai-Ning Liang, Eng Gee Lim, Zhun Shen, Chi-Un Lei,<br>Tomas Krilavičius, Yue Yang, Lixin Cheng, Vladimir Hahanov, and Igor Yemelyanov | 91  |

| Synthesis of Qubit Models for Logic Circuits<br>Wajeb Gharibi, Zaychenko S.A., Dahiri Farid, Hahanova Yu.V., Guz O.A.,<br>Ngene Christopher Umerah, Adiele Stanley                                                                                                                   | 95  |

| Theory of Optimal Nonlinear Filtering in Infocommunication's Problems<br>Victor V. Panteleev                                                                                                                                                                                         | 102 |

| Verification of Specifications in the Language L with respect to Temporal<br>Properties Expressible by GR(1) Formulas<br><b>Anatoly Chebotarev</b>                                                                                                                                   | 110 |

| Properties of code with summation for logical circuit test organization<br>Anton Blyudov, Dmitry Efanov, Valery Sapozhnikov, Vladimir Sapozhnikov                                                                                                                                    | 114 |

| Loop Nests Parallelization for Digital System Synthesis<br>Alexander Chemeris, Julia Gorunova, Dmiry Lazorenko                                                                                                                                                                       | 118 |

| Decreasing the Power Consumption of Content-Addressable Memory<br>in the Dataflow Parallel Computing System<br>Levchenko N.N., Okunev A.S., Yakhontov D.E., Zmejev D.N.                                                                                                              | 122 |

| WebALLTED: Interdisciplinary Simulator Based on Grid Services<br>Zgurovsky M., Petrenko A., Ladogubets V., Finogenov O., Bulakh B.                                                                                                                                                   | 126 |

| Malfunctions Modeling of Converters and Homogeneous-chain Distributed Structure Devices<br>Artur Gulin, Zhanna Sukhinets                                                                                                                                                             | 130 |

| On structure of quasi optimal algorithm of analogue circuit designing Zemliak A., Michua A., Markina T.                                                                                                                                                                              | 134 |

| A Neuro-Fuzzy Edge Based Spectrum Sensing Processor for Cognitive Radios<br>Mohammadreza Baharani, Mohammad Aliasgari, Mohammadreza {Najafi, Jamali},<br>Hamid Noori                                                                                                                 | 138 |

| Qubit Model for Solving the Coverage Problem<br>Hahanov V.I., Litvinova E.I., Chumachenko S.V., Baghdadi Ammar Awni Abbas,<br>Eshetie Abebech Mandefro                                                                                                                               | 142 |

| PDF testability of the circuits derived by special covering ROBDDs with gates <b>Matrosova A., Nikolaeva E., Kudin D., Singh V.</b>                                                                                                                                                  | 146 |

| Compositional Microprogram Control Unit with Operational Automaton of Transitions<br>Alexander Barkalov, Roman Babakov, Larisa Titarenko                                                                                                                                             | 151 |

| Observability Calculation of State Variable Oriented to Robust PDFs and LOC or LOS Techniques Matrosova A., Ostanin S., Melnikov A., Singh V.                                                                                                                                        | 155 |

# **Compositional Microprogram Control Unit** with Operational Automaton of Transitions

Alexander Barkalov\*, Roman Babakov\*\*, Larisa Titarenko\* \*University of Zielona Gora, Poland \*\*Donetsk National Technical University, Ukraine E-mail: cpld@mail.ru

#### Abstract

The using of operational automaton of transitions as the block of microinstruction addressing of compositional microprogram control unit is proposed. The new structure model of compositional microprogram control unit with reduced hardware amount is developed. The generalized structure of operational automaton of transitions is suggested. An example of process of synthesis of compositional microprogram control unit with operational automaton of transitions is given.

#### 1. Introduction

A control unit is used in a vast majority of digital systems [1]. Nowadays, we witness the tremendous growth for the complexity of problems to be solved by digital systems. It requires development new, more effective methods for synthesis of control units. One of the most important problems in this area is the development of design methods leading to decreasing the cost of a resulting system.

If a control algorithm of a digital system is represented by a linear graph-scheme of algorithm (GSA), then the model of compositional microprogram control unit (CMCU) [2] can be used for implementing the corresponding control unit. A CMCU can be viewed as a composition of automata with "hardwired" and "programmable" logic. The overwhelming majority of transitions in CMCU are executed using a counter. But transitions depended on logical conditions are executed using a combinational circuit having irregular nature [2]. The methods of CMCU's synthesis are based on constructing so-called operational linear chains (OLC). The transitions within the same OLC are executed using the counter. The transitions between different OLCs are executed using special block of microinstruction addressing (BMA).

There are many approaches leading to decreasing the hardware amount (logical gates quantity) in logic circuit of BMA. As a rule, these methods are based on multilevel organization of BMA [3, 4]. But these methods result in decreasing for performance of CMCU. For many practical tasks, the performance of digital system should be as high as possible. So, the methods of multilevel organization can't be used here.

The authors proposed a design method for reduction of hardware amount in the logic circuit of finite-state machine (FSM) [5]. It is based on usage of a special operational automaton of transitions (OAT) for generating codes of next states. In this article we propose using this approach for CMCU. It can result in decreasing the hardware amount in comparison with known methods of CMCU design.

# 2. Organization of CMCU with operational automaton of addressing

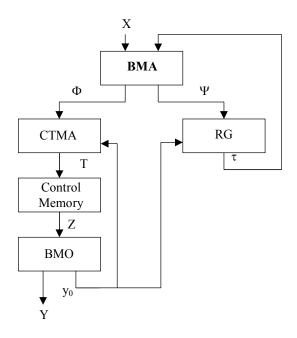

The base model of CMCU is shown in Fig. 1. Let us denote this model as  $U_1$ .

In CMCU  $U_1$ , the block BMA and register RG form an FSM S1. It executes transitions between outputs and inputs of OLCs in line with the following system

$$\Phi = \Phi (\tau, X). \tag{1}$$

In the system (1), the set  $\tau$  includes logical variables  $\tau_r \in \tau$  used for encoding states  $b_m \in B$ , where  $B = \{b_1, ..., b_{Mo}\}$  is a set of states of FSM S1. The number of variables in  $\tau$  is determined as

$$R_{\rm B} = \lceil \log_2 M_0 \rceil. \tag{2}$$

The second component of the equation (1) is the set of logical conditions  $X=\{x_1, ..., x_L\}$ . Each conditional vertex of GSA  $\Gamma$  contains one element of X. The transitions between states of FSM S1 are determined by the system

$$\Psi = \Psi (\mathbf{\tau}, \mathbf{X}). \tag{3}$$

Let us point out that  $|\mathbf{\tau}| = |\Psi| = R_A$  and  $|\Phi| = R$ . The value of R is determined as

$$R = \lceil \log_2 M \rceil. \tag{4}$$

In (4), the value M is equal to the number of operator vertices in GSA  $\Gamma$  (it is the same as the number of microinstructions kept into the control memory).

Figure 1. The base model of CMCU

The counter of microinstruction address (CTMA), the control memory (CM) and the block of microoperations (BMO) form a microprogram control unit (MCU) S2 with natural addressing of microinstructions [6]. The MCU S2 executes transitions between microinstructions corresponding operator vertices from the same OLC. Such a transition is executed by incrementing the CTMA's content due to variable  $y_0=1$ . The block BMO is used for generating microoperations  $y_n \in Y$ , where  $Y = \{y_1, ..., y_n \in Y\}$  $y_N$  is a set of microoperations. The BMO is necessary if some method of encoding of collections of microoperations is used [6]. The BMO generates also a variable y<sub>0</sub>. If y<sub>0</sub>=1, then the FSM S1 does not change its state and addressing of microinstructions is executed by CTMA. If  $y_0=0$ , then the output of some OLC is reached. In this case, the FSM S1 generates new values of functions (1) and (3) and a transition between outputs and inputs of OLCs is executed.

The drawback of CMCU  $U_1$  is an irregular structure of logic circuit of BMA [2]. It is implemented using

such "small" elements as, for example, LUT elements of FPGA [7]. We propose using standard operational blocks (OB) such as adders, shifters and so on for implementing BMA. These blocks are standard library elements of CAD systems [8, 9] and their circuits are optimized. Usage of standard blocks leads to decreasing the design time and increasing the reliability of resulting projects.

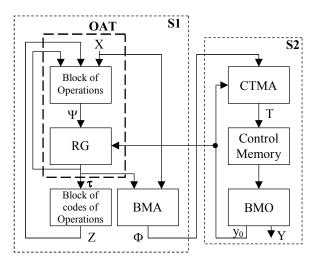

Let us introduce an operational automaton of transitions (OAT) in CMCU  $U_1$ . In this case the system (3) includes both arithmetical and logical operations. It leads to CMCU  $U_2$  shown in Fig. 2.

Figure 2. Structure diagram of CMCU U<sub>2</sub>

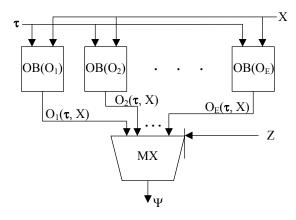

The block BO has the following structure (Fig. 3).

Figure 3. Structure diagram of block of operations

In BO, the symbol OB(O<sub>e</sub>) stands for the operational block executing some operation  $O_e \in O$  ( $e = \overline{1, E}$ ). The symbol  $O_e(\tau, X)$  means the outcome of operation  $O_e \in O$ . The multiplexor MX is used for

transferring the proper code to form correct values of the functions  $\Psi$ . The choice is determined by variable  $z_r \in Z$  from BCO.

The proposed method can be used if the total hardware amount in the circuit of S1 for CMCU  $U_2$  is less than for its counterpart from  $U_1$ . This fact can be proved either by results of design for both  $U_1$  and  $U_2$  or by some formula. These problems are beyond the scope of this article.

#### 4. Investigation of CMCU with OAT

Let us use the minimum hardware amount as an efficiency criterion for CMCU  $U_2$ . Let us find the efficiency  $E_{U_2}$  of CMCU  $U_2$  in comparison with CMCU  $U_1$  as the following relation:

$$E_{U_2} = \frac{H_{U_1}}{H_{U_2}}.$$

(5)

In (7),  $H_{U_1}$  is a hardware amount in logic circuit of BMA in CMCU  $U_1$  used for implementing the system (3);  $H_{U_2}$  is a hardware amount in logical circuit of OAT in  $U_2$ . Obviously, if there is  $E_{U_2} > 1$ , then CMCU with OAT needs less amount of hardware than CMCU  $U_1$ .

According to our investigations, the next generalized dependences of hardware amount are discovered:

$$H_{U_1} = H_1(R, R_{LC}, T, k_1), \quad (6)$$

$$H_{U_2} = H_2(R, R_{LC}, T, k_2). \quad (7)$$

In (8) and (9), the following symbols are used:

R is the number of bits of address of microinstruction;

$R_{LC}$  is the average number of logical conditions analyzed in the same transition;

T is the number of transitions in GSA (equal to the number of conjunctive terms in system (3) for CMCU  $U_1$ );

$k_1$  is a coefficient of minimization of complexity for the equations of system (3) for structure U<sub>1</sub> due to the usage of some standard optimization methods of Boolean equations ( $k_1 = \overline{0,1}$ );

$k_2$  is a coefficient defined as relation of the average hardware amount for one OT in CMCU U<sub>2</sub> to hardware amount required for one term in system (3) in CMCU U<sub>1</sub>. According to (5)-(7), several dependences of  $E_{U_2}$  from these parameters are obtained by the authors. Let us overview some of them for the following values: R=10, R<sub>LC</sub>=2, T=2000, k<sub>1</sub>=0,8, k<sub>2</sub>=30.

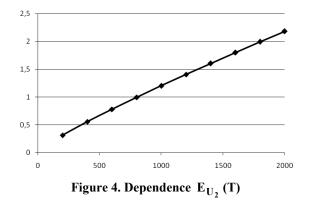

The function  $E_{U_2}(T)$  is shown in Fig. 4. As follows from Fig. 4, this function is linear. The CMCU  $U_2$  becomes more effective when there is T>800. The further growth of the number of transitions leads to the growth of the gain.

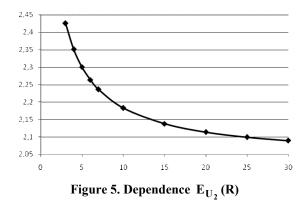

The function  $E_{U_2}(R)$  is shown in Fig. 5. Analysis of Fig. 5 shows that this function is restricted by the value 2,05. So, the logic circuit of CMCU U<sub>2</sub> always needs less hardware then the logic circuit of CMCU U<sub>1</sub>.

We do not show the function  $E_{U_2}(k_1)$  because of its linear nature. If  $k_1=1$  (no minimization is possible), then  $E_{U_2}$  reaches its maximum value equal to 2,73. Only in the case when usage of minimization simplifies the system (3) up to 60% (reducing up to 40% of logical gates), the application of CMCU U<sub>1</sub> makes sense. The function  $E_{U_2}(k_2)$  is shown in Fig. 6. As follows from the Fig. 6, the growth of average complexity of operational blocks used for executing transitions leads to decreasing of efficiency  $E_{U_2}$ . For values of arguments, our approach can be applied till  $k_2$ <65.

Figure 6. Dependence  $E_{U_2}(k_2)$

Analysis of functions shown on Fig. 4 – Fig. 6 allows determine the main factors providing increase for efficiency of CMCU  $U_2$ : the growth of number of transitions, the decrease the length of address of microinstruction, and the implementing control algorithms with small rate of minimization.

#### **5.** Conclusions

In this article we propose using an operational automaton for executing transitions in CMCU. It allows using standard library elements of CAD tools in CMCU design. This approach can decrease the hardware amount because the same operational element can be used for executing a lot of transitions. Also, the process of design is simplified due to use of standard library elements such as adders, shifters, incrementors, multiplexors and so on.

As we can see from achieved experimental results, using the operational automaton of transitions can reduce hardware amount of logical circuit of CMCU by several times in comparison with base model of CMCU.

There are some directions for development of the proposed approach. We should develop a method for constructing the set of operations leading to decrease of hardware amount in the operational automaton of transitions. Next, some optimization method should be developed for further hardware decrease in the logical circuit of CMCU with OAT.

#### 6. References

[1] Baranov S. Logic and system design of digital systems. – Tallinn: TUT Press, 2008. – 266 pp.

[2] Barkalov A., Titarenko L. Logic Synthesis for Compositional Microprogram Control Units. – Berlin: Springer, 2008. – 272 pp.

[3] Wisniewski R. Synthesis of compositional microprogram control units with programmable devices. – Zielona Gora: UZG Press, 2009. – 146 pp.

[4] Barkalov A., Titarenko L. Code conversion in compositional microprogram control units // Cybernetics and System Analysis. V. 47, № 5, 2011. – pp. 763-772.

[5] Barkalov A., Babakov R. Operational formation of state codes in microprogram automata // Cybernetics and System Analysis. V. 47, № 2, 2011. – pp. 193-197.

[6] Barkalov A., Wegrzyn M. Design of Control Units with Programmable Logic. – Zielona Gora: UZ Press, 2006. – 150 pp.

[7] Maxfield C. The Design Warrior's Guide to FPGAs. – New Jersi: Elsevier. – 2004. – 542 pp.

[8] Altera Corporation, 2012. Available at: <www.altera.com>

[9] Xilinx Inc., 2012. Available at: <www.xilinx.com>